In the previous tutorial, basics of sequential logic circuits were discussed. It was mentioned that sequential circuits can be of two types – synchronous and asynchronous. Sequential circuits are different from combinational circuits in the way they have memory elements for feedback from previous input states. Asynchronous circuits use latches as memory elements. Latches cannot be used as memory elements in synchronous circuits, as synchronous circuits require transition-sensitive devices to operate against clock signals. So, for synchronous circuits, flip-flops are used as memory elements.

The flip-flops themselves are built on latches. To make a flip-flop, the operation of the basic latch is modified by providing an additional control input that determines when the state of the circuit should be changed. So basically the latch with the additional control input is called a flip-flop. The additional control input is the clock or enable input.

Flip-flops are categorized into different types depending on how their inputs and clock pulses cause the transition between two states. There are four basic types of flip-flops as follows –

1 ) S–R Flip-Flop

2 ) J–K Flip-Flop

3 )D Flip Flop

4 ) T flip-flop

SR flip-flop –

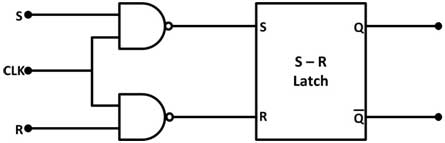

The SR flip-flop is simply the SR latch with enable input. The SR lock with Enable input was described in the previous tutorial. This is the simplest flip-flop. The SR latch is constructed by two cross-coupled NOR gates. The Enable input is added by connecting two additional NAND gates to the basic SR latch circuit. Thus, the SR flip-flop has two outputs Q and Q' that are complementary to each other and three inputs – Set (S), Reset (R) and Enable (En). The clock pulse is applied to the enable input. The flip-flop changes state only when it is set to HIGH (if the Enable input is active high) or when it is set to LOW (if the Enable input is active low). The enable input can be activated low by connecting an inverter port before it. The Flip Flop SR has the following logic gate diagram –

![]()

Fig. 1: SR flip-flop logic gate diagram

It can be represented by the following block diagram –

Fig. 2: SR flip-flop block diagram

It operates according to the following function table –

Figure 3: Truth table of the SR flip-flop

It can be seen from the function table that when S = 0 and R = 0 the output of NAND gates 3 and 4 is forced to become 1. Therefore, R' and S' will be equal to 1. Since S' and R ' are the input of the basic SR latch using NAND gates, there will be no change in the state of the outputs. When S = 0 and R = 1, since S = 0, the output of NAND-3, i.e., R' = 1 and E = 1, the output of NAND-4, i.e., S' = 0. Therefore, Qn+1 = 0 and Qn+1 bar = 1. This is called reset disease. When S = and R = 0. output of NAND-3 i.e. R' = 0 and output of NAND-4 i.e. S' = 1. Therefore, the output of SR NAND latch is Qn+1 = 1 and Qn+1 bar = 0. This is called the set condition. Since S = 1, R = 1 and E = 1, the output of both NAND gates 3 and 4 is 0, that is, S' = R' = 0. Therefore, the prohibited condition will occur in the basic NAND latch.

D flip-flop –

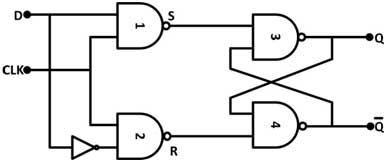

The D Flip Flop is constructed from the D latch. It is designed to avoid prohibited conditions in the SR flip-flop. The D (Delay) flip-flop has only one input called the delay input, the two outputs Q and Ǭ and the Enable input to receive clock pulses. AD Flip Flop is built by coupling inputs to NAND gates in an SR Flip Flop. By coupling NAND gates at the first level of the logic gate implementation of the D Flip Flop, the Data input is directly connected to the Set (S) input of the SR latch while it is connected via an inverter to the Reset (R) input of the SR latch . Thus, when Data (D) is 0, Set is 0 and Reset is 1, whereas when D is 1, Set is 1 and Reset is 0. The AD flip-flop has the following logic gate diagram –

Fig. 4: D flip-flop logic gate diagram

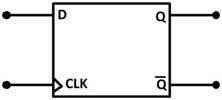

The AD flip-flop can be represented by the following logic gate diagram –

Fig. 5: Block diagram of D flip-flop

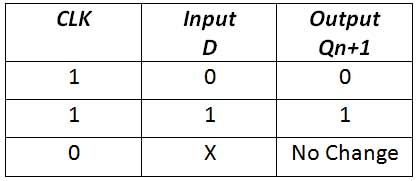

The D Flip Flop operates according to the following table of functions –

Figure 6: D flip-flop truth table

From the function table, it can be seen that when the CLK input is at a LOW level, the D input has no effect, as the set and reset inputs of the NAND slipper are kept HIGH. When CLK goes HIGH, output Q will take the value of input D. If CLK = 1 and D = 1, the NAND -1 gate output goes to 0, which is the S-bar input of the basic NAND-based SR flip-flop and NAND gate-2 goes to 1, which is the R-bar input of the basic NAND-based SR flip-flop . Therefore S bar = 0 and R bar = 1, the output will be 1, that is, it follows the input D. For CLK = 1 and D = 0, the output will be 0. If D changes while CLK is HIGH, Q will follow and change quickly.

From the function table it is clear that the next state of the flip-flop at any time (Qn +1) follows the value of input D when the clock pulse is applied. Since the transfer of data from input to output is delayed, this is known as delay (D) flip-flop. The D flip-flop is used as a delay device or as a latch to store 1 bit of binary information.

Slave master JK slipper –

The Master Slave JK flip-flop was designed to avoid prohibited conditions in the SR flip-flop, in addition to eliminating the timing problem for responding to high and low levels of the clock pulse. The Master Slave JK Flip-Flop is built by connecting two SR flip-flops in cascade with feedback from the output of the second to the input of the first. This way, the Master flip-flop is triggered by a positive level. But due to the presence of the inverter on the clock line, the slave will respond to the negative level. Therefore, when the clock signal is 1 (positive level), the master is active and the slave is inactive. When the clock is at 0 (low level), the slave is active and the master is inactive.

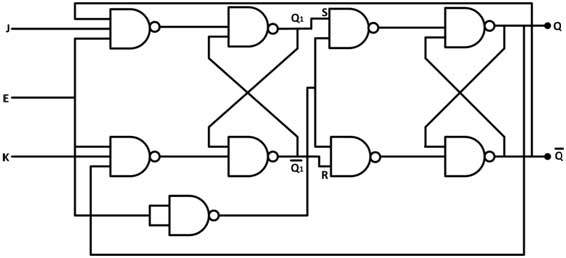

The JK flip-flop has three inputs J, K and Enable input, while two outputs Q and Q'. The JK Flip Flop has the following logic gate diagram –

Fig. 7: Logic gate diagram of the Master Slave JK flip-flop

It operates according to the following function table –

Fig. 8: Truth Table of Flip Flop Master Slave JK

From the table function it can be seen that there are four possible outputs of JK flip flops as mentioned below –

Case 1 – J. = K = 0 (No change): When the clock signal is 0, the slave is active and the master is inactive. But since the S and R inputs have not changed, the slave outputs will also remain unchanged. Therefore, the outputs will not change if J and K are 0.

Case 2 – J. = 0 and K = 1 (Reset): When the Clock signal is 1, the Master is active while the slave is inactive. Therefore, the master outputs become Q1 = 0 and Q1 bar = 1. This means that S becomes 0 and R becomes 1. When the Clock signal is 0, the Slave is active while the master is inactive . Therefore, the slave outputs become Q = 0 and Q bar = 1. Again, when the clock signal is 1, the Master is active and the slave is inactive. Therefore, even with the changed outputs (Q = 0 and Q bar = 1) fed back to the master, its output will be Q1 = 0 and Q1 bar = 1. This means that S becomes 0 and R becomes 1. Therefore, with clock signal being 0 and the slave becoming active, the slave outputs will remain Q = 0 and Q bar = 1. Thus, there is a stable output from the Master and Slave.

Case 3 – J. = 1 and K = 0 (Set): When the Clock signal is 1, the Master is active and the slave is inactive. Therefore, the master outputs become Q1 = 1 and Q1 bar = 0. This means that S is set to 1 and R is set to 0. When the Clock signal is 0, the Slave is active and the Master is inactive. Therefore, the slave outputs become Q = 1 and Q bar = 0. Again, when the clock signal is 1, it can be seen that the slave outputs are stabilized at Q = 1 and Q bar = 0.

Case 4 – J. = K = 1 (Toggle): When the Clock signal is 1, the Master is active and the slave is inactive. The master outputs will be switched. So S and R will also be inverted. When the Clock signal is 0, the Slave is active and the Master is inactive. The slave outputs will be switched. These changed outputs are returned to the master inputs. But when the clock signal is 0, the master is still inactive. Therefore, it does not respond to these changed outputs. This avoids multiple switching that leads to race around condition. The master slave flip-flop is useful to avoid the race condition of the SR flip-flop.

T slipper –

The T flip-flop or Toggle Flip Flop changes its output at each clock transition. It is another basic flip-flop that has just a single data input (T), a clock input and two outputs Q and Ǭ. The T-type flip-flop is built from the JK flip-flop by connecting its J and K inputs. The T represents the ability of the flip-flop to toggle or complement its state. AT Flip Flop is represented by the following block diagram –

Fig. 9: T flip-flop block diagram

The T Flip Flop can be constructed by connecting the J and K inputs of the JK flip flop together. In this way, the JK flip-flop can only enter the no-change state or the toggle state. The T Flip Flop is constructed from the JK Flip Flop as follows –

Fig. 10: T flip-flop logic gate diagram

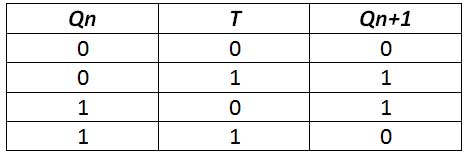

The T Flip Flop operates according to the following table of functions –

Fig. 11: T flip-flop truth table

From the function table, it can be seen that when the input T is in 0 state (that is, J = K = 0) before clock pulse, the output Q will not change with timing . When the input T is set to 1 level (i.e. J = K = 1) before timing , the output will be in the Ǭ state after clocking. In other words, if input T is logic 1 and the device is synchronized, the output will change state regardless of which output was before the input. timing . So, when T = 0, then Qn+1 = Qn, i.e. the next state is equal to the current state and no change occurs. When T = 1, then Qn+1 = Ǭn , that is, the state of the flip-flop is complemented. This is called toggle, so the flip-flop got the name T flip-flop.

Flip-Flops are an essential part of any synchronous circuit. They can store a single bit at a time. Groups of flip-flops are used to store data in practical synchronous circuits. In the next tutorial, learn about registries .