In the previous two tutorials, we learned about VHDL Fundamentals and Programs . Next, we will simulate and verify VHDL programs.

To edit, compile, run (simulate), or verify a VHDL program, there are requirements that include software tools such as:

- XILINX ISE

- ModelSim by Mentor Graphics

- Aldec Riviera

- Quartus-II of Altera etc.

All of these are commercial simulators. Here we will use Altera's MAX+II VHDL simulator, designed for educators and students.

To get started, follow the step-by-step procedure to build and simulate the VHDL program for any digital circuit using MAX+II.

Step 1

Open the MAX+II software from the start menu. The following screen will appear on your computer screen:

Step 2:

Create a new file in the file -> new menu. A new dialog box will open. From here, select the text editor file and click OK.

This will open the text editor in which you can write the VHDL program.

Step 3:

Let's start with the simple half-adder program. Write the following code in the editor area and click save.

ENTITY half_adder IS

PORT (a, b: IN BIT;

sum, carry: OUT BIT);

END half_adder;

half_adder_arch ARCHITECTURE OF half_adder IS

TO START

sum <= a xor b;

carry <= a and b;

END half_adder_arch;

Step 4:

Save the program file by clicking the save button (or the file –> save menu). The save dialog box will appear. Select the appropriate directory and folder (for example, here it is: E:\vhdl_programs\half_adder)

Note: It is advisable to create a new folder for each new VHDL program in the directory. Additionally, there must be NO space (““) in the full path of the VHDL program.

Give the file the same name as the entity name, “ medium_adder ” and select the .vhd extension as per this screenshot.

After saving your work, you will see that all the keywords such as “ ENTITY”, “IS”, “ARCHITECTURE ”, etc. are all highlighted.

Step 5:

Then you will have to set this project as active. To do this, go to file –> project –> set project to current file.

You will notice that MAX+plus II will set the project for the current file to half_adder.

Step 6:

Now compile the MAX+PLUS II – > compiler file. The compiler will appear on the screen. Press start to start the compilation.

When the compilation is complete, it should indicate 0 errors and 0 warnings. Just click OK to complete the compilation.

Step 7:

Now we have to create one more file which is a waveform editor file, which will give us the results as input-output waveforms. To create the waveform editor file, go to MAX+II –> waveform editor.

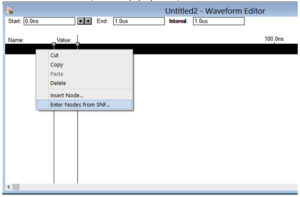

The following waveform editor window will open:

Step 8:

Right click on the blank area. Then, in the pop-up menu, select “insert SNF node”.

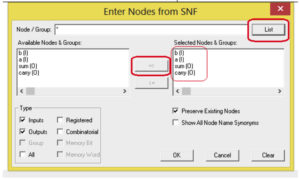

The new dialog box will appear. First, select “list” and then the '=>' button before clicking OK.

You will see all the input-output signal waveforms. The ' a', 'b', 'sum' and ' load' will appear in the waveform editor window similar to this image.

Here, the 'xx' lines indicate the output signals that you cannot edit. But you can edit input signals 'a' and 'b'.

Step 9:

Then zoom out the waveform by pressing the zoom out button on the left side of the screen.

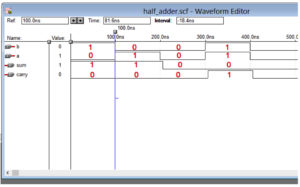

Now enter the values of 'a' and 'b' as '1' and '0' by selecting the area (just press and hold the mouse button to select the area). Make sure to select the value 1 or 0 on the left side.

Set the values 1 or 0 of 'a' and 'b' as desired. Make all four combinations 00, 01, 10 and 11 as shown here:

Step 10:

Save the waveform file. By default, its name will be “ half_adder.swf ”. Click OK.

Step 11:

Then, access the MAX+II – > simulator to simulate the work here.

Click start in the simulator dialog box. When the simulation is successful, the dialog box will appear with 0 errors and 0 warnings.

Step 12:

Click OK and open the wavefrom editor file to check the half adder result.

This procedure must be followed to edit, compile, simulate, and verify all VHDL programs.

The next tutorial will cover the simulation of different digital circuits in VHDL when using MAX + II.