The AVR (ATmega32) contains some built-in registers for TWI communication that not only reduce the level of complexity but also facilitate the entire communication process.

These records have been explained in this tutorial.

1. TWBR (TWI bitrate register):

|

TWBR7

|

TWBR6

|

TWBR5

|

TWBR4

|

TWBR3

|

TWBR2

|

TWBR1

|

TWBR0

|

This register is used in master mode to set the bitrate generator division factor (SCL clock frequency). The bitrate generating unit controls the time period of the SCL. The SCL clock frequency is decided by the Bit Rate Register (TWBR) and the prescaler bits of the TWSR register (explained below).

two. TWSR (TWI status record):

|

TWS7

|

TWS7

|

TWS7

|

TWS7

|

TWS7

|

–

|

TWPS1

|

TWPS0

|

· Bits7-3 – TWS: TWI Status

These bits reflect the TWI bus status which will be explained later in the code explanation. The article focuses only on the status conditions that will be used in the codes. For more details on the rest of the status, see the datasheet.

· Bit 2- Reserved bit

· Bits1-0 – TWPS: TWI Prescaler Bits

These bits are used to set the 'Bitrate Generating Unit' prescaler.

|

TWPS1

|

TWPS0

|

Pre-Climber Value

|

|

0

|

0

|

1

|

|

0

|

1

|

4

|

|

1

|

0

|

16

|

|

1

|

1

|

64

|

Prescaler value according to TWPS bits

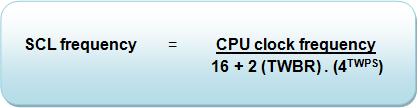

Formula for SCL clock frequency:

Fig. 1: Image showing the formula for SCL clock frequency

3. TWDR (TWI data record):

|

TWD7

|

TWD6

|

TWD5

|

TWD4

|

TWD3

|

TWD2

|

TWD1

|

TWD0

|

The TWDR always contains the latest data present on the SDA bus. In transmitter mode, the TWDR contains the next byte to be transmitted. While in receive mode, the TWDR contains the last received byte. Data in TWDR remains stable as long as the TWINT flag is high.

Continuous

4. TWCR (TWI control register):

|

TWINT

|

TWEA

|

TWSTA

|

TWSTO

|

TWWC

|

TWELVE

|

–

|

TWO

|

· Bit 7 – TWINT: TWI interrupt flag

This bit is used to monitor the current status of the TWI. TWINT is set by hardware when TWI finishes its current work. The SCL will be low until the TWINT bit is set. The TWINT flag must be cleared by the software before starting any operation on the TWI.

Note: The TWINT flag is cleared by writing a logical to it.

· Bit 6 – TWEA: TWI enable acknowledgment bit

The TWEA bit is used to generate the acknowledgment pulse. If the TWEA bit is written to one, the ACK pulse will be generated. And on the other hand, if the TWEA bit is zero, the device can be virtually temporarily disconnected from the two-wire serial bus.

Note: TWI status values are different when data is transferred based on receiving the ACK (TWEA is set) or NOT ACK (TWEA is clear) pulse.

· Bit 5 – TWSTA: TWI START Condition Bit

By writing one to this bit, the device becomes a master controller. It checks whether the bus is available (the bus is not busy transmitting to other masters) and then generates the start condition on the bus. If the bus is not free, the TWI waits until a STOP condition is detected and then generates a new START condition to claim to be the bus master.

· Bit 4 – TWSTO: TWI STOP Condition Bit

By writing one to the TWSTO bit, the master will generate a STOP condition on the two-wire serial bus. When the STOP condition is executed on the bus, the TWSTO bit is automatically cleared.

· Bit 3 – TWWC: TWI Write Collision Flag

This bit is used to avoid collision when writing to the TWDR. The TWWC bit will be set when the TWDR is trying to write (the TWINT flag is low). The TWWC flag is cleared by writing TWDR when TWINT is high.

· Bit 2 – TWEN: TWI enable bit

The TWEN bit is used to enable/disable the TWI interface. When this bit is written to one, TWI operation is enabled. If this bit is written to zero, TWI will be turned off and TWI transmission will be terminated.

· Bit 1 – Bit reserved and always written as zero.

· Bit 0 – TWIE: TWI interrupt enable

The TWIE bit is used to enable/disable the TWI interrupt request. The interrupt request is enabled by writing a one to it and disabled by writing a zero to it.

5. TWAR (TWI address record (slave)):

|

TWA6

|

TWA5

|

TWA4

|

TWA3

|

TWA2

|

TWA1

|

TWA0

|

TWGCE

|

· Bits 7-1 – TWA: TWI (slave) address bits

These bits are used to store 7-bit slave addresses that the TWI responds to when programmed as a Slave Transmitter or Receiver.

· Bit 0 – TWGCA: TWI General Call Recognition Enable Bit

This bit is used to allow the slave to recognize the general call address (0x00).

The general call addresses all devices on the bus using the I 2 Address C 0.

If a device doesn't need the information provided, it simply won't do anything. The devices that process the message recognize this address and behave as slave receivers.

The master cannot detect how many devices are using the message. The second byte contains a command.

See also the TWI interface with the ATmega32