Note: It is recommended to follow this series of VHDL tutorials in order, starting with the first tutorial .

In the previous tutorial VHDL Tutorial – 11 we learned how to design half subtractor and full subtractor circuits using VHDL.

In this tutorial, we will:

- Write a VHDL program to build an 8-bit parity generator and checker circuits

- Check the program output waveform (like a digital circuit) with the truth table of the parity generator and parity checker circuits

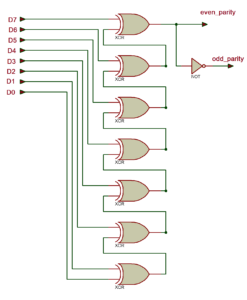

The 8-bit parity generator circuit

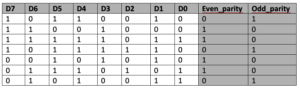

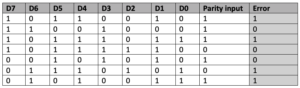

Truth table

Note: here not all 256 combinations of D0-D7 are displayed. Only a few are taken as examples.

Now, let's write, compile and simulate a VHDL program to obtain a waveform output. Then we will check the waveform output with the given truth table.

Before you begin, be sure to review the step-by-step procedure provided in VHDL Tutorial – 3 to properly design the project, as well as edit and compile the program and waveform file, including the final output.

VHDL Program

ieee library;

use ieee.std_logic_1164.all;

entity parity is

port(data:in bit_vector(7 to 0);

par_p,odd_p: output bit);

final parity;

parity_gen parity architecture is

signal temperature: bit_vector (5 to 0);

to start

temp(0)<=data(0) xor data(1);

temp(1)<=temp(0) xor data(2);

temp(2)<=temp(1) xor data(3);

temp(3)<=temp(2) xor data(4);

temp(4)<=temp(3) xor data(5);

temp(5)<=temp(4) xor data(6);

par_p <= temp(5) xor data(7);

strange_p <= not(temp(5) xor data(7));

end parity_gen;

Observation:

- The “entity” describes the input-output connections of the digital circuit. According to the circuit given here, there is an 8-bit data input of 'd0-d7' and two outputs of 'even_p' and 'odd_p.'

- The “architecture” describes the operation of the circuit, which means how the output is generated from a given input.

To refresh your memory on how this works, read the first two VHDL tutorials ( 1 and 2 ) in this series.

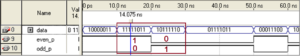

Next, compile the above program, creating a waveform file with all the necessary inputs and outputs listed, and simulate the project. You should get the following result…

Check the output waveforms 'even_p' and 'odd_p' with the input data of 'D0-D7.' For example, as highlighted in the diagram, for the input “1111 1011”, the even_p output is '1' and the odd _p output is '0.' For input “1011 1110”, the even_p output is '0' and the odd_p output is '1.'

Now, let's build the 8-bit parity checker circuit.

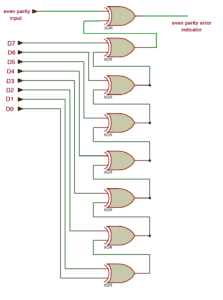

The 8-bit parity checker circuit

Truth table

VHDL Program

ieee library;

use ieee.std_logic_1164.all;

parity_chk entity is

port(data:in bit_vector(7 to 0);

p: in bits;

e: outside the bit);

end parity_chk;

parity_arch architecture of parity_chk is

signal temperature: bit_vector (6 to 0);

to start

temp(0)<=data(0) xor data(1);

temp(1)<=temp(0) xor data(2);

temp(2)<=temp(1) xor data(3);

temp(3)<=temp(2) xor data(4);

temp(4)<=temp(3) xor data(5);

temp(5)<=temp(4) xor data(6);

temp(6) <= temp(5) xor data(7);

e <= p xor temp(6);

end parity_arch;

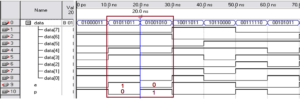

Simulation waveforms

Check the output waveform 'e' with the parity input 'p' and data 'D0-D7.' For example, as highlighted in the diagram, for input “0101 1011” and parity '1', the error output is '1.' For input “0100 1010” and parity '0', the output is '0.'

In the next tutorial, we will learn how to design 8×3 encoder and 3×8 decoder circuits using VHDL.