In digital systems, any information is represented by binary codes. There are many binary code systems, as mentioned in the first tutorial in this series. An n-bit binary code can represent 2 n discrete symbols or elements of encoded information. The digital circuits that perform the encoding of digital information are called encoders, while the digital circuits that decode the encoded digital information are called decoders. An encoder with enabled pins is called a multiplexer, while a decoder with enabled pins is called a demultiplexer.

The encoder, decoder, multiplexer and demultiplexer are combinational logic circuits as their output at any time depends on the combination of input signals present at that instant only and does not depend on any past conditions. Let's learn about each one in this tutorial.

Decoders –

Decoders are used to decode binary information in a digital system. The input lines to a decoder are used to feed binary data, while based on the binary data, one of the output lines is selected, representing the respective minterm. If a decoder has n input lines, it can have at most 2 n output lines. With n number of input lines, the decoder can decode n-bit digital data. As with 3 input lines, a decoder can decode 3-bit binary data and therefore a maximum of 2 3 or 8 binary symbols. If there are some unused combinations in the n-bit encoded information, the decoder may have less than 2n lines of output. Therefore, any decoder is an n-to-m line decoder, where m <= 2n .

In a decoder, each output line represents a minterm that is selected based on the input binary data. For any given input data, only one output line is activated at a time. It can be noted that in a decoder the number of output lines is always greater than the number of input lines. If the number of inputs and outputs in a decoder circuit is equal, it is called a converter.

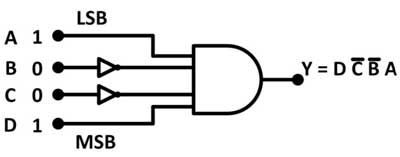

Decoders are generally built using AND or NAND gates. The output of an AND gate is only HIGH when all inputs are HIGH. Therefore, the AND gate is the basic decoding element in a decoder circuit. For example, in a 4 to 16 line decoder, the digital circuit used in decoding the binary code 1001 will be as follows –

Fig. 1: Image showing the decoding circuit built using AND Gate

In the decoding element (from 4 to 16 line decoder) shown above, to make all AND gate inputs HIGH, the middle two bits must be inverted using two NOT gates. Therefore, when the input binary data is 1001, the single output line connected to the above decoding circuit will be activated and set to HIGH.

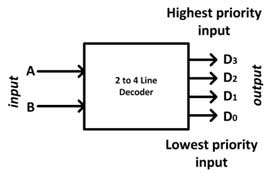

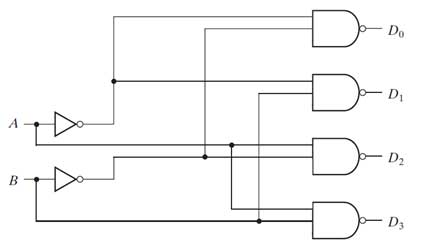

For simplicity, let's take the 2 to 4 line decoder as an example. A 2 to 4 line decoder has two input lines (say A and B). With 2 inputs, 4 binary codes can be represented, so there can be 4 output lines (say D0, D1, D2 and D3). Each output line represents a minterm such as D0 represents A'B', D1 represents A'B, D2 represents AB' and D3 represents AB. A 2 to 4 line decoder can be represented by the following block diagram –

Fig. 2: Block diagram of the 2 to 4 line decoder

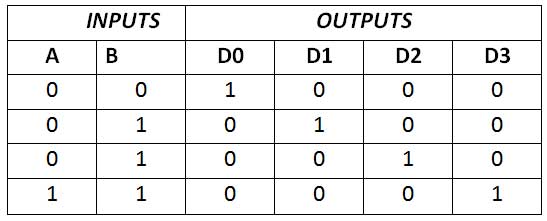

You will have the following truth table –

Fig. 3: Truth table of the 2 to 4 line decoder

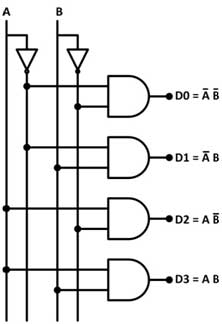

From the truth table above, the digital circuit for the 2 to 4 line decoder can be constructed using AND gates and NOT gates as follows –

Fig. 4: Circuit diagram of 2 to 4 line decoder

If a decoder is built using NAND gates, then the respective output line will be set to LOW instead of HIGH for a binary code. For example, the digital circuit for 2 to 4 line decoder built using NAND gates will be as follows –

Fig. 5: Image showing the implementation of the 2 to 4 line decoder with NAND gates

Decoders are used in many applications like data demultiplexing, digital display, digital to analog converters, memory addressing, etc.

Demultiplexers –

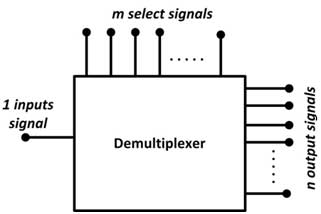

Demultiplexers are digital circuits used to transmit binary data from one line to many. The word “demultiplexer” itself means one in many. Therefore, demultiplexing is the process of taking information from one input and passing it through one of multiple outputs. Demultiplexers have similar digital circuitry to decoders, except that they have a single input line and have selected lines to determine the output line for data transmission. Data is transmitted over a single output line at a time. Just like the decoder, if a demultiplexer has n select lines, there can be 2 n or fewer output lines controlled by them in a demultiplexer. A demultiplexer can be represented by the following block diagram –

Fig. 6: Demultiplexer block diagram

It can be noted that a demultiplexer has an input signal, m selection signals and n output signals where n <= 2 l . The selected inputs determine which output line the data input will be connected to. With the help of a demultiplexer, serial data is converted into parallel data.

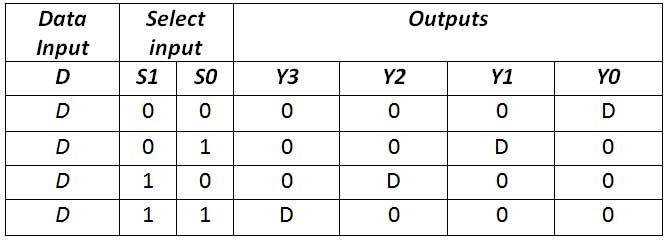

For example, in a 1 to 4 line demultiplexer, there is a single input (say D), four outputs (say Y0 to Y3) and two select lines (say S1 and S2). The truth table of the 1 to 4 line demultiplexer is as follows –

Fig. 7: Demultiplexer Truth Table

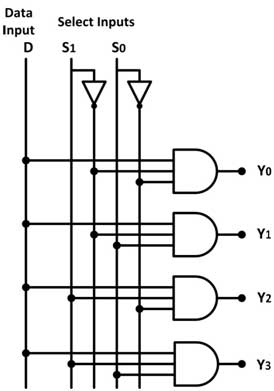

From the truth table, it can be seen that the data input is connected to the output Y0 when S1 = 0 and S0 = 0. The data input is connected to the output Y1 when S1 = 0 and S0 = 1. The input of Data input is connected to output Y2 when S1 = 1 and S0 = 0. Data input is connected to output Y3 when S1 = 1 and S0 = 1. A demultiplexer can be constructed using AND gates and NOT gates as the decoder circuits. In the truth table above, the digital circuit for the 1 to 4 line demultiplexer is as follows –

Fig. 8: 4-output demultiplexer circuit diagram

Therefore, the 1-to-4 line demultiplexer can be implemented using four 3-input AND gates and two NOT gates. The input data line is connected to all AND gates. The two selection lines S1 and S0 enable only one port at a time and the data that appears on the input line passes through the selected port to the associated output line.

Demultiplexers are used in communication systems, computer chips for connecting ALUs to registers, and in serial-to-parallel converters.

Encoders –

Encoders are used to encode binary data. They are the opposite of decoders. Therefore, they perform reverse operation of a decoder. The opposite of the decoding process is called encoding. The encoder is a combinational logic circuit that converts an active input signal into a coded output signal.

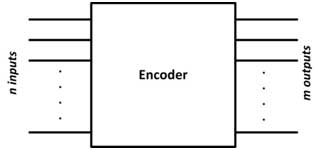

It has n input lines, only one of which is active at any time in output lines. It encodes one of the active inputs into an m-bit encoded binary output. In an encoder, the number of output lines is less than the number of inputs. If an encoder has n lines of input in lines of output, then n<= 2 l . An encoder can be represented by the following block diagram –

Fig. 9: Encoder block diagram

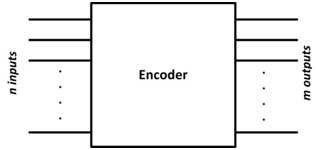

For example, let's consider Priority Encoder. It is a special type of encoder in which priority is given to the input lines. If two or more input lines are HIGH at the same time, then the input line with the highest priority will be considered. In a 4 to 2 line priority encoder, there are four inputs, say D0, D1, D2 and D3, and two outputs, Y0 and Y1. Of the four inputs, D3 has the highest priority and D0 has the lowest priority. This means that if D3 = 1 then Y1 Y0 will be equal to 11 regardless of the other inputs. Similarly, if D3 = 0 and D2 = 1, then Y1 Y0 will be equal to 10 regardless of the other inputs. A 4 to 2 line priority encoder can be represented by the following block diagram –

Fig. 10: 4-input priority encoder block diagram

There is the following truth table –

Fig. 11: Truth table of the 4-input priority encoder

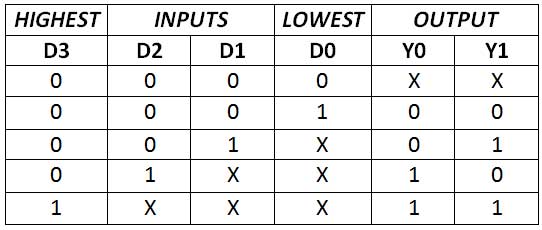

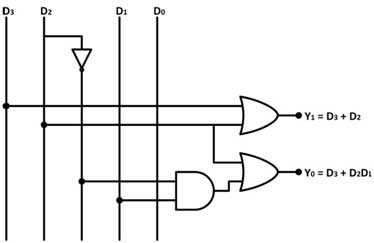

An encoder can be constructed using AND, OR and NOT gates. From the truth table above, the digital logic circuit for 4 to 2 line encoder can be designed as follows –

Fig. 12: Circuit diagram of 4-input priority encoder

Multiplexers –

Multiplexers are used to route digital data from many to one line. They convert parallel data to serial data. The term multiplex itself means many to one. Multiplexing is the process of transmitting a large number of information over a single line.

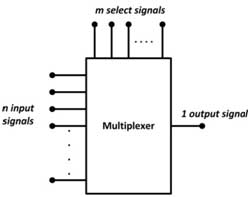

A digital multiplexer is a combinational circuit that selects unique digital information from multiple resources and transmits the selected information on a single output line. A multiplexer is also called a data selector, where it selects one of the many inputs and sends the information to the output. Multiplexers are similar to encoders except they have multiple data input lines and a single output line. The selection of a specific input line is controlled by a set of selection lines. A multiplexer can be represented by the following block diagram –

Fig. 13: Multiplexer block diagram

It can be noted that a multiplexer has n input lines, m selection signals and one output line where n <= 2 l . The selection line decides the number of input lines of a specific multiplexer. If the number of n input lines is equal to 2 i , then m selection lines are required to select one of the n input lines. For example, to select one of 4 input lines, two selection lines are required, and to select one of 8 input lines, 3 selection lines are required.

As in a four-input multiplexer, there are four data input lines (say D0 to D3), a single output line (say Y) and two select lines (say S0 and S1) to select one of the four input lines . A 4-input multiplexer can be represented by the following block diagram –

Fig. 14: Block diagram of the 4-input multiplexer

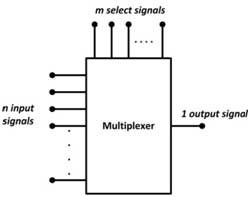

There is the following truth table –

Fig. 15: Truth table of the 4-input multiplexer

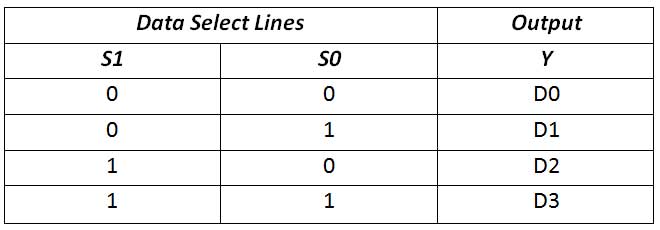

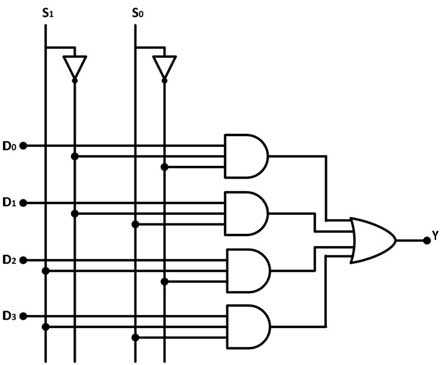

A multiplexer circuit is similar to the encoder circuit. Just like encoders, multiplexers can be built using AND, OR and NOT gates. From the truth table above, the logic gate diagram for 4 input multiplexer is as follows –

Fig. 16: Circuit diagram of 4-input multiplexer

From the logic circuit, it can be seen that when S1S0 equals 00 is applied to select rows, the two AND gate inputs associated with D0 are equal to 1 and the third input is connected to D0 data. The other 3 AND gates have 0 in at least one of their inputs, so their outputs will be equal to 0. Therefore, the OR output Y will be equal to D0. When S1S0 equal to 01 is applied to selected lines, data from input D1 appears on the data output line. Similarly, when S1S0 equal to 10 is applied to the selected rows, the data from input D2 appears in the data output row. When S1S0 equal to 11 is applied to the selected lines, the data from input D3 appears on the data output line.

Multiplexers are used in telephony, communication systems and computer memories. They are also used as parallel to serial data converters.

In the next tutorial, learn how to design encoder and decoder circuits using 7400 series logic gate ICs.