En un tutorial anterior VHDL Tutorial 3, aprendimos cómo diseñar, simular y verificar cualquier circuito digital en VHDL utilizando el software simulador VHDL MAX+II de Altera.

(Si no sigue esta serie de tutoriales de VHDL uno por uno, se le pedirá que revise todos los tutoriales anteriores de esta serie antes de continuar con este tutorial)

En este tutorial,

- Escribiremos un programa VHDL para construir todos los puertos digitales.

- Simular el programa para diseñar circuitos digitales para todos los puertos.

- Verifique la forma de onda de salida del programa (circuito digital) con la tabla de verdad de estas PUERTAS lógicas

Comencemos con el circuito digital para el cual escribiremos un programa VHDL.

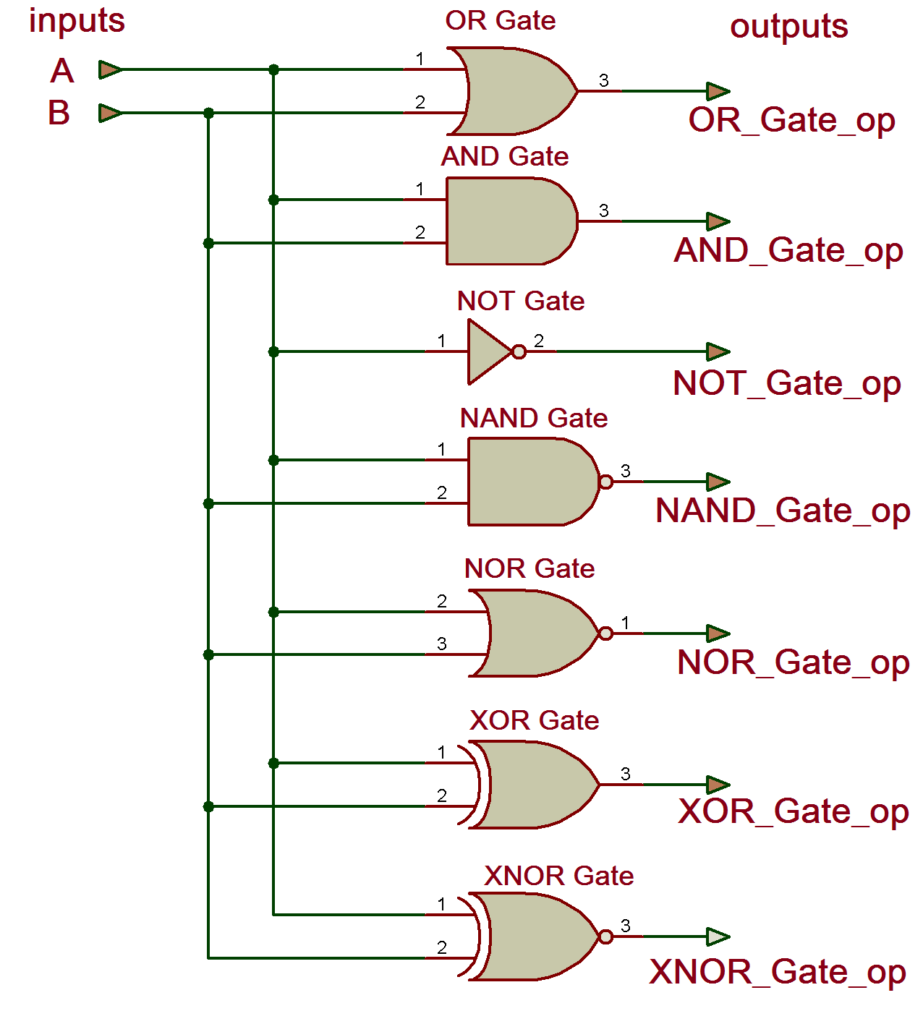

Circuito digital

Aquí está la tabla de verdad para el circuito anterior.

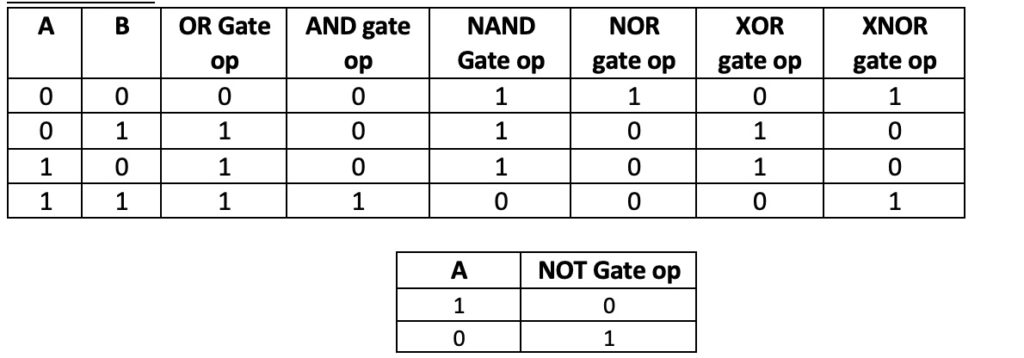

Aquí está la tabla de verdad para el circuito anterior.

Mesa de la verdad

Ahora escribamos un programa VHDL, compilémoslo, simulémoslo y obtengamos el resultado en forma de onda. Finalmente, verificaremos estas formas de onda de salida con la tabla de verdad proporcionada.

Ahora escribamos un programa VHDL, compilémoslo, simulémoslo y obtengamos el resultado en forma de onda. Finalmente, verificaremos estas formas de onda de salida con la tabla de verdad proporcionada.

(Siga el procedimiento paso a paso proporcionado en el tutorial anterior (Tutorial VHDL 2) para crear un proyecto, editar y compilar un programa, crear un archivo de forma de onda, simular el programa y generar formas de onda de salida).

Programa VHDL

biblioteca IEEE;

utilice IEEE.STD_LOGIC_1164.ALL;

La entidad logic_gate es

Puerto (A,B: en std_logic;

y_and,y_or,y_nand,y_nor,y_not,y_xor,y_xnor: fuera de std_logic);

finalizar logic_gate;

La arquitectura all_gates de logic_gate es

para comenzar

y_and <= a y b;

tu_tu <= a o b;

y_nand <= a nand b;

y_nor <= a ni b;

y_not <= no es uno;

y_xor <= a xor b;

y_xnor <= a xnor b;

terminar all_gates;

“ entidad ” describe las conexiones de entrada-salida del circuito digital. Según nuestro circuito anterior, solo tenemos dos entradas 'A' y 'B' y 7 salidas para 7 puertos.

La “ arquitectura ” describe el funcionamiento del circuito; significa cómo se genera la salida a partir de una entrada determinada.

(Para aprender más y obtener más detalles sobre los programas VHDL, lea los dos primeros tutoriales VHDL Tutorial 1 y VHDL Tutorial 2 de esta serie).

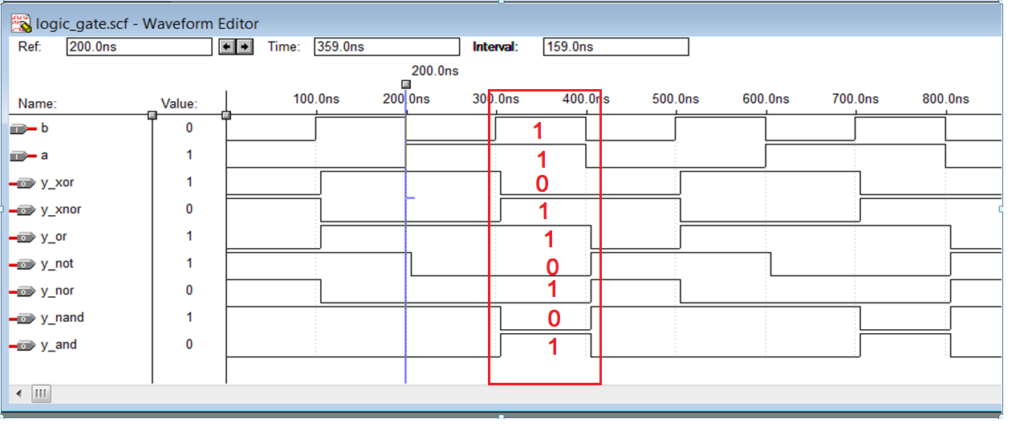

A continuación, compile el programa anterior (cree un archivo de forma de onda con todas las entradas y salidas enumeradas), simule el proyecto y obtendrá el siguiente resultado:

Forma de onda de simulación

Ahora verifique estas formas de onda de salida con la tabla de verdad de GATE. Por ejemplo, aquí se resalta un caso con las entradas A=1 y B=1. También puedes consultar los otros tres casos.

Ahora verifique estas formas de onda de salida con la tabla de verdad de GATE. Por ejemplo, aquí se resalta un caso con las entradas A=1 y B=1. También puedes consultar los otros tres casos.

Así es como puedes construir un circuito lógico GATE simple en VHDL y verificar su salida con su tabla de verdad.

En el siguiente tutorial veremos cómo construir puertas NAND, NOR, XOR y XNOR usando tres puertas básicas Y, O y SIN usar VHDL.