Nota: Se recomienda seguir esta serie de tutoriales de VHDL en orden, comenzando con el primer tutorial .

En el tutorial anterior, Tutorial VHDL – 21, diseñamos un circuito sumador completo de 8 bits usando VHDL.

En este tutorial, vamos a:

- Escriba un programa VHDL que construya un circuito comparador de 1 y 8 bits.

- Verifique la forma de onda de salida del programa (circuito digital) con el funcionamiento del circuito comparador

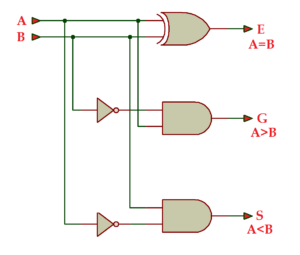

El circuito comparador de 1 bit

Mesa de la verdad

Ahora escribamos, compilemos y simulemos un programa VHDL. Luego obtendremos la salida de la forma de onda y la verificaremos con la tabla de verdad proporcionada.

Antes de comenzar, asegúrese de revisar el procedimiento paso a paso proporcionado en el Tutorial VHDL – 3 para diseñar el proyecto. Esto asegurará que edite y compile correctamente el programa y el archivo de forma de onda, así como el resultado final.

Programa VHDL

biblioteca IEEE;

utilice IEEE.STD_LOGIC_1164.ALL;

La entidad comparador_1bit es

Puerto (A,B: en std_logic;

G,S,E: salida std_logic);

comparador final_1bit;

La arquitectura comp_arch de comparador_1bit es

para comenzar

G <= A y (no B);

S <= (no A) y B;

E <= A xnor B;

comp_arch final;

Puede resultar útil revisar los dos primeros tutoriales de VHDL ( 1 y 2 ) de esta serie para refrescar su memoria sobre cómo funciona.

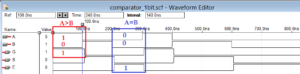

Luego compile el programa anterior, creando y guardando un archivo de forma de onda con todas las entradas y salidas requeridas enumeradas (asegurándose de que se apliquen todas las combinaciones de entradas diferentes). Luego simule el proyecto. Deberías obtener el siguiente resultado...

Según esta figura, las salidas de 'G' y 'E' están resaltadas en rojo y azul respectivamente para A>B y A=B.

A continuación, ampliaremos esto de un comparador de 1 bit a un comparador de 8 bits. Para hacer esto usando VHDL, emplearemos un estilo de modelado de comportamiento porque es más fácil que los otros dos estilos.

El programa comparador VHDL de 8 bits

biblioteca IEEE;

utilice IEEE.STD_LOGIC_1164.ALL;

La entidad comparador_8bit es

Puerto (A,B: en std_logic_vector(0 a 7);

G,S,E: salida std_logic);

comparador final_8bit;

La arquitectura comp_arch de comparador_8bit es

para comenzar

proceso

para comenzar

si A=B entonces

GRAMO <= '0';

S <= '0';

mi <= '1';

elsif A>B entonces

GRAMO <= '1';

S <= '0';

mi <= '0';

elsi A

GRAMO <= '0';

S <= '1';

mi <= '0';

terminara si;

fin del proceso;

comp_arch final;

Forma de onda de simulación

Como se muestra en esta figura, los tres resultados están resaltados en rojo, azul y verde, lo que representa A>B, A

Este es el tutorial final de esta serie VHDL. Puede encontrar programas adicionales para diferentes circuitos digitales en línea y practicarlos para obtener más experiencia práctica con la programación VHDL. ¡Sigue aprendiendo y seguirás progresando!