Nota: Se recomienda seguir esta serie de tutoriales de VHDL en orden, comenzando con el primer tutorial .

En el tutorial anterior, Tutorial VHDL – 19, diseñamos un contador binario de 4 bits usando VHDL.

En este tutorial, vamos a:

- Escriba un programa VHDL para construir un conversor de código binario a gris y de gris a binario de 4 bits

- Verifique la forma de onda de salida del programa (circuito digital) con la tabla de verdad del convertidor de códigos

El conversor de código binario a gris de 4 bits

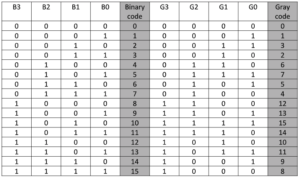

Mesa de la verdad

Ahora escribamos, compilemos y simulemos un programa VHDL. Luego obtendremos la salida de la forma de onda y la verificaremos con la tabla de verdad proporcionada.

Antes de comenzar, asegúrese de revisar el procedimiento paso a paso proporcionado en el Tutorial VHDL – 3 para diseñar el proyecto. Esto asegurará que edite y compile correctamente el programa y el archivo de forma de onda, así como el resultado final.

Programa VHDL

biblioteca ieee;

utilice ieee.std_logic_1164.all;

La entidad b2g_code es

puerto (b: en std_logic_vector(3 a 0);

g: salida std_logic_vector(3 a 0));

finalizar b2g_code;

La arquitectura b2g_arch de b2g_code es

para comenzar

g(3) <=b(3);

g(2) <= b(3) xor b(2);

g(1) <= b(2) xor b(1);

g(0) <= b(1) xor b(0);

finalizar b2g_arch;

Puede resultar útil revisar los dos primeros tutoriales de VHDL ( 1 y 2 ) de esta serie para refrescar su memoria sobre cómo funciona.

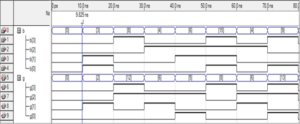

Luego compile el programa anterior, creando y guardando un archivo de forma de onda con todas las entradas y salidas requeridas enumeradas (asegurándose de que se apliquen todas las combinaciones de entradas diferentes). Luego simule el proyecto. Deberías obtener el siguiente resultado...

Forma de onda de simulación

Es fácil comprobar todas las diferentes combinaciones de la entrada del código binario (b0-b3) con la salida del código gris (g0 – g3). A continuación, haremos el procedimiento inverso. Construiremos un circuito convertidor de código gris a binario.

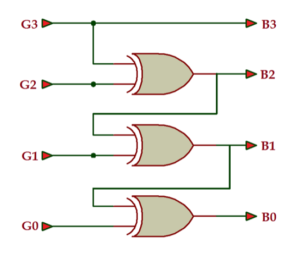

El circuito convertidor de código gris a binario.

Programa VHDL

biblioteca ieee;

utilice ieee.std_logic_1164.all;

La entidad g2b_code es

puerto (g: en std_logic_vector(3 a 0);

b: salida std_logic_vector(3 a 0));

finalizar g2b_code;

La arquitectura g2b_arch de g2b_code es

para comenzar

b(3) <= g(3);

b(2) <= g(3) xorg(2);

b(1) <= g(3) xorg(2) xou g(1);

b(0) <= g(3) xou g(2) xou g(1) xou g(0);

finalizar g2b_arch;

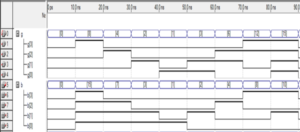

Formas de onda de simulación

De la figura se desprende claramente que la entrada del código gris (g0 – g3) y la salida del código binario (b0 – b3) corresponden a la tabla de verdad dada.

En el próximo tutorial, construiremos un circuito sumador completo de 8 bits usando VHDL.