Nota: Se recomienda seguir esta serie de tutoriales de VHDL en orden, comenzando con el primer tutorial .

En el tutorial anterior, Tutorial VHDL – 14, diseñamos dos circuitos usando VHDL: un demultiplexor 1x8 y un multiplexor 8x1.

En este proyecto vamos a,

- Escriba un programa VHDL para construir un circuito SR Latch (flip-flop) sincronizado

- Verifique la forma de onda de salida del programa (el circuito digital) con la tabla de verdad del circuito flip-flop.

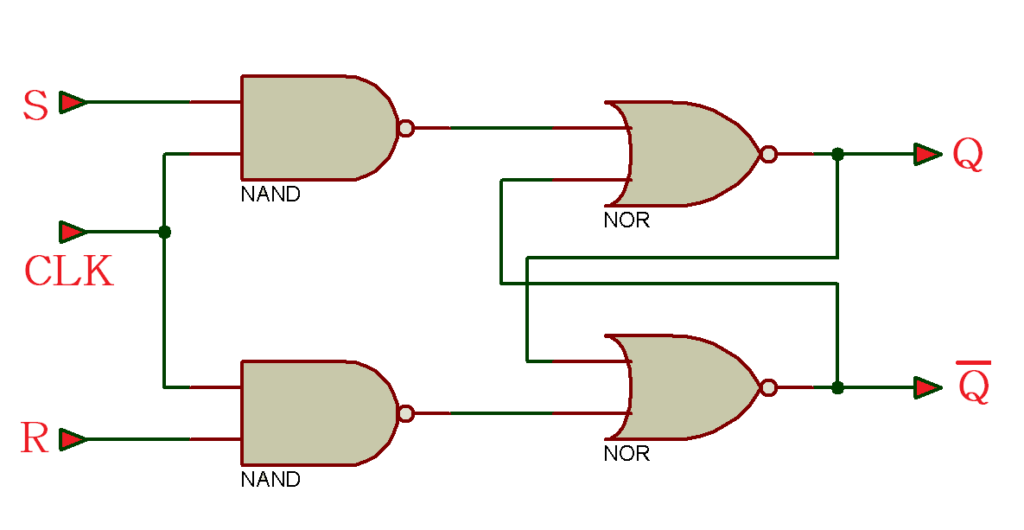

Un circuito de pestillo SR sincronizado:

Mesa de la verdad

Ahora escribamos, compilemos y simulemos un programa VHDL. Luego obtendremos la salida de la forma de onda y la verificaremos con la tabla de verdad proporcionada.

Antes de comenzar, asegúrese de revisar el procedimiento paso a paso proporcionado en el Tutorial VHDL – 3 para diseñar adecuadamente el proyecto, así como editar y compilar el programa y el archivo de forma de onda, incluido el resultado final.

Para este tutorial, utilizamos un estilo de modelado de comportamiento para escribir el programa VHDL que construirá el circuito flip-flop. Este es el estilo de modelado preferido para circuitos digitales secuenciales.

Programa VHDL

biblioteca ieee;

utilice ieee.std_logic_1164.all;

entidad RS_FF es

puerto (clk,r,s: en std_logic;

P: fuera std_logic;

Qnot: fuera std_logic);

finalizar RS_FF;

La arquitectura RSFF_arch de RS_FF es

señal t1,t2: std_logic;

para comenzar

t1 <= r ni t2;

t2 <= s ni t1;

proceso (clk,r,s)

para comenzar

si(clk'evento y clk='1′ ) entonces

si(r='0′ y s='0′) entonces

Q<=t1;

Qno <= t2;

elsif(r='0′ y s='1′) entonces

Q<='1';

Qnot <='0′;

elsif(r='1′ y s='0′) entonces

Q<='0';

Qnot <='1′;

elsif(r='1′ y s='1′) entonces

Q<='X';

Qnot <='X';

terminara si;

terminara si;

fin del proceso;

finalizar RSFF_arch;

Para refrescar su memoria sobre cómo funciona esto, lea los dos primeros tutoriales de VHDL ( 1 y 2 ) de esta serie.

A continuación, compile el programa anterior, cree un archivo de forma de onda con todas las entradas y salidas necesarias enumeradas y simule el proyecto. Deberías obtener el siguiente resultado...

Forma de onda de simulación

Como se muestra en esta figura, cuando la entrada del reloj es '1', entonces "s" es '1'. Y cuando “r” es '0', el flip-flop está configurado, lo que significa que la salida Q es '1' y Qnot es '0'.

Asegúrate de comprobar las diferentes combinaciones con la tabla de verdad proporcionada.

En el próximo tutorial, diseñaremos un flip-flop D usando VHDL.