En el tutorial anterior de VHDL, diseñamos circuitos codificadores de 8 × 3 y decodificadores de 3 × 8 usando VHDL.

(Si no sigue esta serie de tutoriales de VHDL uno por uno, se le pedirá que revise todos los tutoriales anteriores de esta serie antes de continuar con este tutorial)

En este tutorial,

- Escribiremos un programa VHDL para construir circuitos demultiplexores 1×8 y multiplexores 8×1.

- Verifique la forma de onda de salida del programa (circuito digital) con la tabla de verdad de estos circuitos multiplexores y demultiplexores.

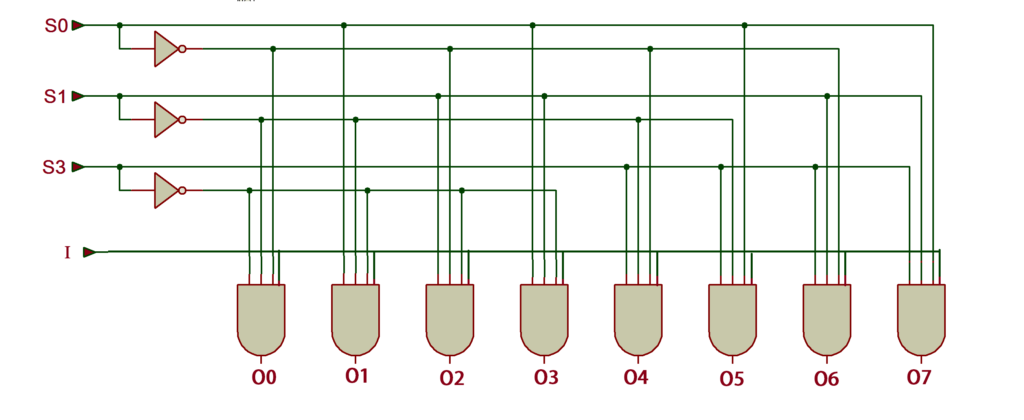

Circuito Demultiplexor 1×8

Mesa de la verdad

(Siga el procedimiento paso a paso proporcionado en el tutorial de VHDL 3 para crear un proyecto, editar y compilar el programa, crear un archivo de forma de onda, simular el programa y generar formas de onda de salida). Ahora escribamos un programa VHDL, compilemos simularlo y obtener la salida en forma de onda. Finalmente, comprobaremos si las formas de onda de salida concuerdan con la tabla de verdad dada.

Utilicé el estilo de modelado de comportamiento para escribir un programa VHDL para construir el demultiplexor porque será más fácil que el estilo de flujo de datos o de modelado estructural.

Programa VHDL

(Para aprender más y obtener más detalles sobre los programas VHDL, lea los dos primeros tutoriales, VHDL Tutorial 1 y VHDL Tutorial 2 de esta serie).

Luego compile el programa anterior – cree un archivo de forma de onda con todas las entradas y salidas enumeradas – aplique diferentes combinaciones de entradas – guarde el archivo de forma de onda y finalmente simule el proyecto. Obtendrá el siguiente resultado.

Simulación de forma de onda

Como se muestra en la figura, se puede observar que cuando las líneas seleccionadas (S2, S1, S0) son “001”, la entrada I=0 está disponible en la salida O1=0, y cuando las líneas seleccionadas son “101” , la entrada I =1 está disponible en la salida O5 = 1. Puede consultar otras combinaciones de líneas seleccionadas con entrada y salida.

A continuación, construiremos un circuito multiplexor de 8×1.

Circuito multiplexor 8×1

Mesa de la verdad

Programa VHDL

Formas de onda de simulación

Formas de onda de simulación

Como se muestra en la figura, se puede observar que para las líneas seleccionadas (S2, S1, S0) “011” y “100”, las entradas d3=1 y d4=1 están disponibles en la salida o=1. Puede consultar otras combinaciones de filas seleccionadas en la tabla de verdad.

En el próximo tutorial, diseñaremos un flip-flop RS sincronizado y un pestillo RS.