Nota: Se recomienda seguir esta serie de tutoriales de VHDL en orden, comenzando con el primer tutorial .

En el tutorial anterior Tutorial VHDL - 11 aprendimos cómo diseñar circuitos de medio restador y de restador completo usando VHDL.

En este tutorial, vamos a:

- Escriba un programa VHDL para construir un generador de paridad de 8 bits y circuitos verificadores.

- Verifique la forma de onda de salida del programa (como un circuito digital) con la tabla de verdad de los circuitos del generador de paridad y del verificador de paridad.

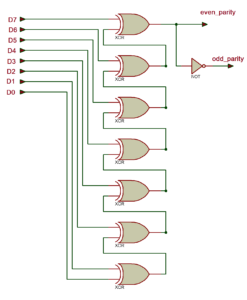

El circuito generador de paridad de 8 bits.

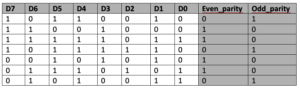

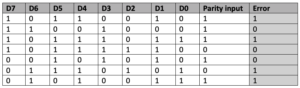

Mesa de la verdad

Nota: aquí no se muestran todas las 256 combinaciones de D0-D7. Sólo unos pocos se toman como ejemplos.

Ahora, escribamos, compilemos y simulemos un programa VHDL para obtener una salida de forma de onda. Luego verificaremos la salida de la forma de onda con la tabla de verdad proporcionada.

Antes de comenzar, asegúrese de revisar el procedimiento paso a paso proporcionado en el Tutorial VHDL – 3 para diseñar adecuadamente el proyecto, así como editar y compilar el programa y el archivo de forma de onda, incluido el resultado final.

Programa VHDL

biblioteca ieee;

utilice ieee.std_logic_1164.all;

la paridad de entidades es

puerto(datos:en bit_vector(7 a 0);

par_p,odd_p: bit de salida);

paridad final;

parity_gen la arquitectura de paridad es

temperatura de la señal: bit_vector (5 a 0);

para comenzar

temp(0)<=datos(0) xor datos(1);

temp(1)<=temp(0) xor datos(2);

temp(2)<=temp(1) xor datos(3);

temp(3)<=temp(2) xor datos(4);

temp(4)<=temp(3) xor datos(5);

temp(5)<=temp(4) xor datos(6);

par_p <= temp(5) xor datos(7);

extraño_p <= not(temp(5) xor data(7));

finalizar parity_gen;

Observación:

- La “entidad” describe las conexiones de entrada-salida del circuito digital. Según el circuito que se proporciona aquí, hay una entrada de datos de 8 bits de 'd0-d7' y dos salidas de 'even_p' y 'odd_p'.

- La "arquitectura" describe el funcionamiento del circuito, es decir, cómo se genera la salida a partir de una entrada determinada.

Para refrescar su memoria sobre cómo funciona esto, lea los dos primeros tutoriales de VHDL ( 1 y 2 ) de esta serie.

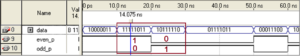

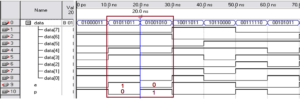

A continuación, compile el programa anterior, cree un archivo de forma de onda con todas las entradas y salidas necesarias enumeradas y simule el proyecto. Deberías obtener el siguiente resultado...

Verifique las formas de onda de salida 'even_p' y 'odd_p' con los datos de entrada de 'D0-D7'. Por ejemplo, como se resalta en el diagrama, para la entrada "1111 1011", la salida par_p es '1' y la salida impar _p es '0'. Para la entrada "1011 1110", la salida par_p es '0' y la salida impar_p es '1'.

Ahora, construyamos el circuito de verificación de paridad de 8 bits.

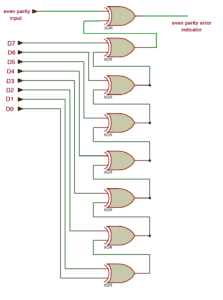

El circuito verificador de paridad de 8 bits

Mesa de la verdad

Programa VHDL

biblioteca ieee;

utilice ieee.std_logic_1164.all;

La entidad parity_chk es

puerto(datos:en bit_vector(7 a 0);

p: en bits;

e: fuera del bit);

finalizar parity_chk;

La arquitectura parity_arch de parity_chk es

temperatura de la señal: bit_vector (6 a 0);

para comenzar

temp(0)<=datos(0) xor datos(1);

temp(1)<=temp(0) xor datos(2);

temp(2)<=temp(1) xor datos(3);

temp(3)<=temp(2) xor datos(4);

temp(4)<=temp(3) xor datos(5);

temp(5)<=temp(4) xor datos(6);

temperatura(6) <= temperatura(5) xor datos(7);

e <= p xor temp(6);

finalizar parity_arch;

Formas de onda de simulación

Verifique la forma de onda de salida 'e' con la entrada de paridad 'p' y los datos 'D0-D7'. Por ejemplo, como se resalta en el diagrama, para la entrada "0101 1011" y la paridad '1', la salida de error es '1'. Para la entrada “0100 1010” y paridad '0', la salida es '0'.

En el siguiente tutorial, aprenderemos a diseñar circuitos codificadores de 8×3 y decodificadores de 3×8 usando VHDL.