SPI ha ganado un papel sólido en los sistemas embebidos, ya sean procesadores system-on-chip, tanto con procesadores de 32 bits de última generación, como los que utilizan ARM, MIC o Power PC, como con otros microcontroladores, como AVR, PIC, etc. Incluye controladores SPI capaces de operar en modo maestro o esclavo. Los controladores AVR programables del sistema se pueden programar mediante una interfaz SPI. Los diseños basados en chips o FPGA a veces utilizan SPI para comunicarse. Así, SPI es una tecnología común utilizada hoy en día para comunicarnos con dispositivos periféricos donde queremos transferir datos de forma rápida y con restricciones en tiempo real. Hay muchas interfaces seriales de telegrafía en código Morse, RS232, USB, Firewire, Ethernet y más. Cada interfaz serie ofrece ventajas o desventajas para muchos diseños, según criterios como la velocidad de datos requerida, la disponibilidad de espacio y las consideraciones de ruido.

La interfaz serie a periférico (SPI) fue una de esas tecnologías desarrollada para reemplazar las interfaces paralelas de modo que no tengamos que enrutar el bus paralelo alrededor de la PCB. Proporciona transferencia de datos de alta velocidad entre dispositivos. Motorola fue la primera empresa en nombrar SPI para una técnica de circuito utilizada a fines de la década de 1970 en su primera MCU basada en 68000 para conectarla a funciones periféricas y luego adoptada por otros en la industria. Es la simplicidad de la interfaz y la velocidad lo que permite la comunicación o la transferencia de datos fácilmente y lo ha convertido en un protocolo de comunicación popular.

La interfaz periférica serie es una interfaz de comunicación serie simple de 4 cables utilizada por muchos chips periféricos de microprocesadores/microcontroladores que permite que los controladores y dispositivos periféricos se comuniquen entre sí. En la interfaz periférica en serie, los datos se transfieren de entrada/salida uno a la vez y se transmiten desde el dispositivo maestro hacia/desde uno o más dispositivos esclavos en distancias cortas y alta velocidad. Simplemente se basa en un registro de desplazamiento de 8 bits que transfiere datos a un solo pin y transfiere datos a otro pin. Otra característica de SPI es que no existe el concepto de transferir la propiedad del bus, es decir, cambiar el maestro y tampoco hay direcciones de esclavo. SPI es un protocolo mucho más sencillo y por eso podemos operarlo a velocidades superiores a los 10MH respecto a TWI. Algunas de las características que permiten el SPI ampliamente utilizado son:

1. Comunicación dúplex completa.

2. Mayor rendimiento que TWI.

3. No limitado a palabras de 8 bits en caso de transferencia de bits.

4. Interfaz de hardware sencilla

5. Elección arbitraria del tamaño, contenido y finalidad de los mensajes.

6. Requisitos de energía típicamente bajos

7. El esclavo utiliza un reloj maestro y no requiere osciladores de precisión.

8. Menores requisitos de energía que TWI debido a menos circuitos.

Sin embargo, sería injusto comparar la interfaz serial TWI con SPI. Cada uno de ellos tiene su área de aplicación dependiendo de las necesidades del sistema, como algunas de las características que hacen que TWI sea tan valioso como SPI.

1. Menos pines en paquetes de circuitos integrados que SPI

2. El control de flujo de hardware está presente

3. Tiene un estándar formal diferente al SPI

4. Acérquese a los esclavos antes de la comunicación.

Ahora que tenemos una breve idea sobre SPI, comprendamos las respuestas a las preguntas de ¿por qué se prefiere SPI en PCB? ¿Cuáles son las conexiones básicas y cómo se comunican? Y por último, ¿cuál es el alcance futuro del SPI?

Por qué se prefiere SPI para PCB

Figura 1: Imagen de bloque que muestra cómo funciona el protocolo SPI

Aunque fue desarrollado principalmente para la comunicación entre el procesador host y los periféricos, también es posible una conexión de dos procesadores a través de SPI. El bus SPI generalmente solo se usa en PCB. Hay muchas razones que nos impiden utilizarlo fuera del campo de los PCB. En primer lugar, SPI fue diseñado para transferir datos entre múltiples chips IC, a velocidades muy altas. Debido a esta alta velocidad, la longitud de las líneas de autobús no debería ser demasiado larga, ya que la reactancia aumenta y el autobús queda inutilizable. Sin embargo, es posible utilizar el bus SPI fuera de la placa de circuito impreso a bajas velocidades, pero esto no es muy práctico. Los periféricos pueden ser relojes en tiempo real, convertidores como ADC y DAC, módulos de memoria como EEPROM y FLASH, sensores como sensores de temperatura y sensores de presión, o algunos otros dispositivos como mezcladores de señales, potenciómetros, controladores LCD, UART, controladores CAN, controladores USB y amplificador.

Líneas de datos y control SPI y conexión básica:

Un protocolo SPI especifica 4 cables de señal.

1. Master Out Slave In (MOSI): la señal MOSI es generada por el maestro, el destinatario es el esclavo.

2. Master In Slave Out (MISO): los esclavos generan señales MISO y el destinatario es el maestro.

3. Reloj serie (SCLK o SCK): la señal SCLK la genera el maestro para sincronizar las transferencias de datos entre el maestro y el esclavo.

4. Selección de maestro-esclavo (SS) a selección de chip esclavo (CS): la señal SS es generada por el maestro para seleccionar dispositivos esclavos/periféricos individuales. El SS/CS es una señal baja activa.

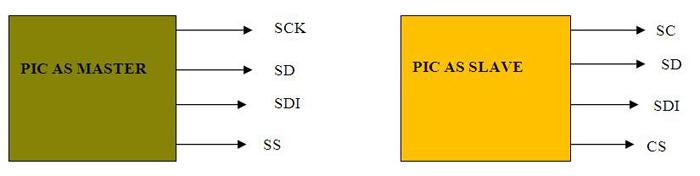

A veces, la entrada de datos en serie (SDI) se utiliza como otro nombre en lugar de MOSI y la salida de datos en serie (SDO) para MISO.

Figura 2: Diagrama de bloques que muestra una aplicación maestra única en el protocolo SPI

Entre estas cuatro señales lógicas, dos de ellas MOSI y MISO se pueden agrupar como líneas de datos y otras dos SS y SCLK como líneas de control.

Un microcontrolador maestro puede comunicarse con múltiples periféricos SPI. Hay 2 formas de configurar cosas:

1. Esclavos en cascada o esclavos encadenados

2. Esclavos independientes o configuración paralela

Configuración de cadena esclava

Configuración de cadena esclava: en la configuración de cadena esclava, todas las líneas de reloj (SCLK) y selección de chip (CS) están conectadas entre sí. Los datos fluyen desde el microcontrolador a cada periférico y de regreso al microcontrolador. La salida de datos del dispositivo esclavo anterior está vinculada a la entrada de datos del siguiente, formando así un registro de desplazamiento más amplio. Por lo tanto, los dispositivos esclavos en cascada se ven evidentemente como un dispositivo más grande y, por lo tanto, reciben la misma señal de selección de chip. Esto significa que sólo se requiere una línea SS desde el maestro, en lugar de una línea SS separada para cada esclavo.

Figura 3: Configuración de cadena esclava en protocolo SPI

Pero debemos recordar que la conexión en cadena no funcionará con dispositivos que admitan o requieran operación multibyte.

Configuración de esclavo independiente:

Esta es la configuración típica de bus SPI con un maestro SPI y múltiples esclavos/periféricos. En esta configuración de esclavo independiente o paralelo,

Todas las líneas de reloj (SCLK) están conectadas entre sí.

2. Todas las líneas de datos MISO están conectadas entre sí.

3. Todas las líneas de datos MOSI están conectadas entre sí.

Figura 4: Diagrama de bloques que muestra el bus SPI en configuración esclava

Figura 5: Diagrama de bloques que muestra varias unidades funcionales en el sistema SPI

Comunicación en SPI

¿Cómo funciona la comunicación en SPI?

La comunicación la inicia el maestro todo el tiempo. El maestro primero configura el reloj usando una frecuencia menor o igual a la frecuencia máxima admitida por el dispositivo esclavo. Ahora, este maestro SPI controla la transferencia de datos generando la señal de reloj (SCLK). Luego, el maestro selecciona el esclavo deseado para la comunicación tirando de la línea de selección de chip (SS) de ese periférico esclavo específico al estado "bajo" y activa el esclavo particular con el que desea comunicarse usando la señal de selección de esclavo (SS). Una vez seleccionado el esclavo, recibe o transmite datos a través de las dos líneas de datos. Un maestro, generalmente el microcontrolador host, siempre proporciona señal de reloj a todos los dispositivos en un bus, ya sea que esté seleccionado o no. Los esclavos en el bus que no hayan sido activados por el maestro usando su señal de selección de esclavo ignorarán el reloj de entrada y las señales MOSI del maestro y no deberían activar MISO. Esto significa que el maestro selecciona sólo un esclavo a la vez.

El uso de cada cuatro pines puede depender de los dispositivos. Por ejemplo, es posible que el pin SDI no esté presente si un dispositivo no requiere una entrada (ADC, por ejemplo), o el pin SDO puede no estar presente si un dispositivo no requiere una salida (controladores LCD, por ejemplo). Si un microcontrolador sólo necesita comunicarse con 1 periférico SPI o un esclavo, entonces el pin CS de ese esclavo se puede conectar a tierra. Con múltiples dispositivos esclavos, se requiere una señal SS independiente del maestro para cada dispositivo esclavo.

¿Qué importancia tiene la producción triestatal en SPI?

En electrónica digital, la lógica de tres estados, tres estados o 3 estados permite que un puerto de salida asuma un estado de alta impedancia más allá de los niveles lógicos 0 y 1, eliminando efectivamente la salida del circuito. Esto permite que varios circuitos compartan la misma línea o líneas de salida (como un bus que no puede escuchar más de un dispositivo al mismo tiempo). La mayoría de los dispositivos/periféricos tienen salidas de tres estados, que pasan al estado de alta impedancia (desconectados) cuando el dispositivo no está seleccionado. Los dispositivos sin estas salidas de tres estados no pueden compartir el bus SPI con otros dispositivos, porque es posible que la selección de chip de ese esclavo no esté activada.

Ahora, si se requiere un período de espera (como para la conversión de analógico a digital), entonces el maestro debe esperar al menos esa cantidad de tiempo antes de comenzar a generar ciclos de reloj. En el maestro SPI, los bits se envían desde el pin MOSI y se reciben en el pin MISO. Los bits a desplazar se almacenan en el registro de datos SPI, SP0DR, y el bit más significativo (bit 7) se envía primero. Cuando el bit 7 del maestro se desplaza a través del pin MOSI, un bit del bit 7 del esclavo se desplaza al bit 0 del maestro a través del pin MISO. Después de 8 pulsos o cambios de reloj, este bit terminará en el bit 7 del maestro. El bit menos significativo se puede enviar primero configurando el bit LSBF en 1 en el registro de control SPI. El reloj que controla la rapidez con la que se transfieren los bits a SP0DR es la señal SCLK. La frecuencia de este reloj puede controlarse mediante el registro de velocidad en baudios SPI, SP0BR. El pin SS debe estar bajo para seleccionar un esclavo. A continuación se muestra un sistema SPI completo.

Figura 6: Descripción general de la comunicación en el sistema SPI con maestro y esclavo

Figura 7: Diagrama que muestra la estructura del esclavo SPI

Un dúplex completo significa que la transmisión de datos puede ocurrir en ambas direcciones durante cada ciclo de reloj. Entonces, cuando el maestro envía un bit por la línea MOSI; el esclavo lee de esa misma línea y el esclavo envía un bit por la línea MISO; el maestro lee en la misma línea. Ahora, para realizar la transferencia de datos, se utilizan registros de desplazamiento organizados con un cierto tamaño de palabra, como 8 bits (pueden ser más), tanto en el maestro como en el esclavo. Están conectados en un anillo. Mientras el maestro transfiere el valor del registro a través de la línea MOSI, el esclavo transfiere los datos a su registro de desplazamiento.

Los datos normalmente se desplazan primero con el bit más significativo del MSB, mientras que el nuevo bit menos significativo del LSB se desplaza al mismo registro. Después de cambiar este registro, el maestro y el esclavo intercambiaron sus valores de registro. Luego, cada dispositivo toma este valor y realiza la operación necesaria con él (por ejemplo, escribirlo en la memoria). Si hay más datos para intercambiar, los registros de desplazamiento se cargan con datos nuevos y se repite el proceso. Cuando ya no hay más datos para transmitir, el maestro detiene el reloj. Normalmente rechaza al esclavo.

Figura 8: Diagrama de bloques que muestra la configuración de hardware para la comunicación entre 2 registros

Hay un "modo de transmisión multibyte" disponible con la interfaz de bus SPI. En este modo, el maestro puede cambiar bytes continuamente. En este caso, la selección de esclavo (SS) se mantiene baja hasta que se completa todo el proceso de flujo.

Los dispositivos SPI a veces usan otra línea de señal para enviar una señal de interrupción a una CPU host. Algunos de los ejemplos de este tipo de señal son las interrupciones del lápiz de los sensores de la pantalla táctil, las alertas de umbral térmico de los sensores de temperatura, las alarmas emitidas por chips de reloj en tiempo real y las inserciones del conector de auriculares del códec de sonido de un teléfono celular.

Polaridad y fase del reloj en SPI.

Significado de la polaridad y fase del reloj:

Otro par de parámetros llamados polaridad del reloj (CPOL) y fase del reloj (CPHA) determinan los bordes de la señal del reloj en los que se conducen y muestrean los datos. Además de configurar la frecuencia del reloj, el maestro también debe configurar medios para ajustar o definir la polaridad del reloj (CPOL) y la fase (CPHA) en relación con los datos. Como el reloj sirve para sincronizar la comunicación de datos, existen cuatro modos posibles que se pueden utilizar en un protocolo SPI, basados en este CPOL y CPHA.

|

Modo |

Polaridad del reloj (CPOL) |

Fase de reloj (CPHA) |

|

SPI_MODE0 |

0 |

0 |

|

SPI_MODE1 |

0 |

1 |

|

SPI_MODE2 |

1 |

0 |

|

SPI_MODE3 |

1 |

1 |

Fig. 9: Diagrama de tiempos SPI usando VHDL

Si la fase del reloj es cero (es decir, CPHA = 0), los datos se retendrán en el flanco ascendente del reloj con CPOL = 0 y en el flanco descendente del reloj con CPOL = 1.

Si CPHA = 1, las polaridades se invierten. Los datos se retienen en el flanco descendente del reloj con CPOL = 0 y en el flanco ascendente con CPOL = 1.

Los microcontroladores le permiten ajustar la polaridad y la fase del reloj. Una polaridad positiva da como resultado que los datos se enganchen en el flanco ascendente del reloj. Sin embargo, los datos se colocan en la línea de datos que ya se encuentra en el flanco descendente para estabilizarse. La mayoría de periféricos, que sólo pueden ser esclavos, funcionan con esta configuración. Si es necesario utilizar la otra polaridad, las transiciones se invertirán.

APLICACIONES SPI

La capacidad full duplex hace que SPI sea muy eficiente para aplicaciones maestro/esclavo. Algunos dispositivos utilizan el modo full-duplex para implementar un flujo de datos rápido y eficiente para aplicaciones como audio digital, procesamiento de señales digitales o canales de telecomunicaciones. SPI se utiliza para comunicarse con varios periféricos como

Sensores: Temperatura, presión, ADC, pantallas táctiles, controladores de videojuegos

Dispositivos de control: Codificación y decodificación de audio, potenciómetros digitales, DAC.

Lentes de cámara: montura de lente Canon EF

Comunicaciones: Ethernet, USB, USART, CAN videojuegos portátiles

Memoria: Flash y EEPROM

Relojes en tiempo real

LCD, a veces incluso para gestionar datos de imágenes

Cualquier tarjeta MMC o SD (incluida la variante SDIO)

Para sistemas de alto rendimiento, los FPGA a veces usan SPI para interactuar como esclavo de un host, como maestro para sensores o para la memoria flash utilizada para la inicialización si están basados en SRAM.

JTAG es esencialmente una pila de aplicaciones para un tipo SPI de tres cables, que utiliza diferentes nombres de señales. SGPIO es esencialmente otra pila de aplicaciones (incompatible) para SPI diseñada para actividades específicas de administración del backplane. SGPIO utiliza mensajes de 3 bits.