El AVR (ATmega32) contiene algunos registros integrados para la comunicación TWI que no sólo reducen el nivel de complejidad sino que también facilitan todo el proceso de comunicación.

Estos registros se han explicado en este tutorial.

1. TWBR (registro de tasa de bits TWI):

|

TWBR7

|

TWBR6

|

TWBR5

|

TWBR4

|

TWBR3

|

TWBR2

|

TWBR1

|

TWBR0

|

Este registro se utiliza en modo maestro para configurar el factor de división del generador de velocidad de bits (frecuencia de reloj SCL). La unidad generadora de velocidad de bits controla el período de tiempo del SCL. La frecuencia del reloj SCL la decide el registro de velocidad de bits (TWBR) y los bits del preescalador del registro TWSR (explicados a continuación).

dos. TWSR (registro de estado TWI):

|

TWS7

|

TWS7

|

TWS7

|

TWS7

|

TWS7

|

–

|

TWPS1

|

TWPS0

|

· Bits7-3 – TWS: Estado TWI

Estos bits reflejan el estado del bus TWI que se explicará más adelante en la explicación del código. El artículo se centra únicamente en las condiciones de estado que se utilizarán en los códigos. Para obtener más detalles sobre el resto del estado, consulte la hoja de datos.

· Bit 2- Bit reservado

· Bits1-0 – TWPS: Bits preescaladores TWI

Estos bits se utilizan para configurar el preescalador de la 'Unidad generadora de velocidad de bits'.

|

TWPS1

|

TWPS0

|

Valor previo al escalador

|

|

0

|

0

|

1

|

|

0

|

1

|

4

|

|

1

|

0

|

dieciséis

|

|

1

|

1

|

64

|

Valor del preescalador según bits TWPS

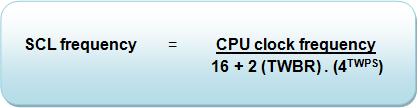

Fórmula para la frecuencia del reloj SCL:

Fig. 1: Imagen que muestra la fórmula para la frecuencia del reloj SCL

3. TWDR (registro de datos TWI):

|

TWD7

|

TWD6

|

TWD5

|

TWD4

|

TWD3

|

TWD2

|

TWD1

|

TWD0

|

El TWDR siempre contiene los últimos datos presentes en el bus SDA. En modo transmisor, el TWDR contiene el siguiente byte a transmitir. Mientras está en modo de recepción, el TWDR contiene el último byte recibido. Los datos en TWDR permanecen estables mientras el indicador TWINT esté alto.

Continuo

4. TWCR (registro de control TWI):

|

GEMELO

|

DOS

|

TWSTA

|

TWSTO

|

TWWC

|

DOCE

|

–

|

DOS

|

· Bit 7 – TWINT: indicador de interrupción TWI

Este bit se utiliza para monitorear el estado actual del TWI. TWINT se configura mediante hardware cuando TWI finaliza su trabajo actual. El SCL estará bajo hasta que se establezca el bit TWINT. El software debe borrar el indicador TWINT antes de iniciar cualquier operación en el TWI.

Nota: El indicador TWINT se borra escribiéndole un código lógico.

· Bit 6 – TWEA: bit de confirmación de activación de TWI

El bit TWEA se utiliza para generar el pulso de confirmación. Si el bit TWEA se escribe en uno, se generará el pulso ACK. Y por otro lado, si el bit TWEA es cero, el dispositivo se puede desconectar prácticamente temporalmente del bus serie de dos hilos.

Nota: Los valores de estado de TWI son diferentes cuando los datos se transfieren según la recepción del pulso ACK (TWEA está configurado) o NOT ACK (TWEA está claro).

· Bit 5 – TWSTA: Bit de condición de ARRANQUE TWI

Al escribir uno en este bit, el dispositivo se convierte en un controlador maestro. Comprueba si el bus está disponible (el bus no está ocupado transmitiendo a otros maestros) y luego genera la condición de inicio en el bus. Si el bus no está libre, el TWI espera hasta que se detecta una condición de PARADA y luego genera una nueva condición de ARRANQUE para reclamar ser el bus maestro.

· Bit 4 – TWSTO: Bit de condición de PARADA TWI

Al escribir uno en el bit TWSTO, el maestro generará una condición de PARADA en el bus serie de dos cables. Cuando se ejecuta la condición STOP en el bus, el bit TWSTO se borra automáticamente.

· Bit 3 – TWWC: Bandera de colisión de escritura TWI

Este bit se utiliza para evitar colisiones al escribir en TWDR. El bit TWWC se establecerá cuando TWDR intente escribir (el indicador TWINT está bajo). El indicador TWWC se borra escribiendo TWDR cuando TWINT es alto.

· Bit 2 – TWEN: bit de habilitación TWI

El bit TWEN se utiliza para habilitar/deshabilitar la interfaz TWI. Cuando este bit se escribe en uno, se habilita la operación TWI. Si este bit se escribe en cero, TWI se desactivará y finalizará la transmisión de TWI.

· Bit 1 – Bit reservado y siempre escrito como cero.

· Bit 0 – TWIE: habilitación de interrupción TWI

El bit TWIE se utiliza para habilitar/deshabilitar la solicitud de interrupción TWI. La solicitud de interrupción se habilita escribiéndole un uno y se deshabilita escribiéndole un cero.

5. TWAR (registro de dirección TWI (esclavo)):

|

TWA6

|

TWA5

|

TWA4

|

TWA3

|

TWA2

|

TWA1

|

TWA0

|

TWGCE

|

· Bits 7-1 – TWA: bits de dirección TWI (esclavo)

Estos bits se utilizan para almacenar direcciones esclavas de 7 bits a las que responde el TWI cuando se programa como transmisor o receptor esclavo.

· Bit 0 – TWGCA: Bit de habilitación de reconocimiento de llamada general TWI

Este bit se utiliza para permitir que el esclavo reconozca la dirección de llamada general (0x00).

La llamada general se dirige a todos los dispositivos del bus utilizando la dirección I 2 C 0.

Si un dispositivo no necesita la información proporcionada, simplemente no hará nada. Los dispositivos que procesan el mensaje reconocen esta dirección y se comportan como receptores esclavos.

El maestro no puede detectar cuántos dispositivos están usando el mensaje. El segundo byte contiene un comando.

Ver también la interfaz TWI con el ATmega32