Como la miniaturización electrónica ha sido un objetivo constante de los fabricantes de chips, los sistemas informáticos/electrónicos basados en placas base finalmente fueron reemplazados por circuitos integrados System-on-Chip (SoC) y Package-on-Package (PoP). Los sistemas informáticos complejos ahora se condensan en teléfonos inteligentes y otros dispositivos portátiles. Estos sofisticados dispositivos y aparatos electrónicos tienen un SoC en su núcleo que gestiona el cálculo y el control completos. El paquete SoC se compone de múltiples núcleos de propiedad intelectual (IP). Estos núcleos IP provienen de diferentes proveedores y empresas de diseño de chips.

La comunicación de datos escalable, compatible y eficiente entre múltiples núcleos IP en un SoC ha sido un desafío. Inicialmente, esto lo hicieron los diseñadores de chips mediante un laborioso rediseño, pruebas de compatibilidad y diseño de interfaz adicional. Este enfoque carecía de coherencia a primera vista, lo que llevó a costosos rediseños futuros. Una de las soluciones viables y ampliamente aceptadas a este problema fue introducida por Arm en 1996 como protocolos AMBA.

¿Qué es AMBA?

AMBA (Arquitectura avanzada de bus de microcontrolador) es un estándar abierto y de libre acceso para interconectar y administrar núcleos IP en un IC System-on-Chip (SoC). Permite el desarrollo inmediato de diseños de chips multiprocesadores de forma modular, reutilizable y escalable. Esto ayuda a evitar costosos rediseños y reduce el tiempo de comercialización de diseños integrados.

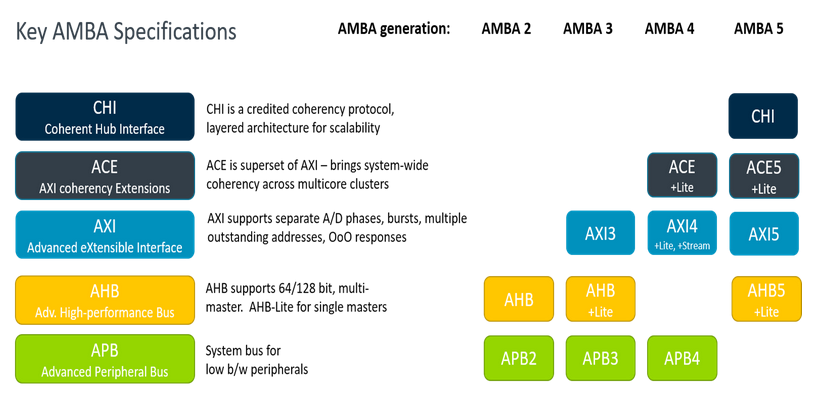

AMBA se introdujo por primera vez en 1996 con especificaciones Advanced Peripheral Bus (APB) y Advanced System Bus (ASB). La segunda versión de AMBA se introdujo en 1999 e incluía especificaciones de bus avanzado de alto rendimiento (AHB). AMBA 3, que incluía la interfaz extensible avanzada (AXI), se introdujo en 2003. AMBA 4 introdujo las extensiones de coherencia AXI (ACE) en 2010 y AMBA 5, la última versión de AMBA, introdujo la interfaz Coherent Hub (CHI) en 2013.

sistema de autobuses AMBA

sistema de autobuses AMBA

Un diseño de SoC tradicional basado en AMBA utiliza especificaciones de bus de sistema avanzado (ASB) o bus avanzado de alto rendimiento (AHB) para comunicación de gran ancho de banda con bloques como el procesador, la RAM en el chip, las interfaces de memoria y el bus DMA maestro. Aunque utiliza Advanced Peripheral Bus (APB) para comunicación de bajo ancho de banda con bloques como UART, GPIO, teclado, display, temporizador, etc., los SoC que tienen una gran cantidad de bloques funcionales o núcleos IP requieren una interconexión punto a punto que utiliza especificaciones de interfaz extensible avanzada (AXI). El bus AXI gestiona la comunicación mediante un protocolo maestro-esclavo y se puede conectar fácilmente al APB. Puede haber varios maestros y esclavos AXI compartiendo un bus.

Los teléfonos móviles y smartphones que contienen SoC con múltiples núcleos de procesador que comparten una memoria caché común requieren una gestión de coherencia en todo el subsistema de memoria. Con este fin, las especificaciones ACE se introdujeron en AMBA 4. Las especificaciones AXI/ACE se rediseñaron como CHI para gestionar mecanismos de comunicación en sistemas informáticos heterogéneos. Por el contrario, para el protocolo basado en señales en las especificaciones AXI/ACE, CHI es un protocolo en capas basado en paquetes que se puede extender a mecanismos de comunicación entre bloques funcionales heterogéneos, como procesadores de señales digitales (DSP), unidades de procesamiento de gráficos (GPU), I. /O subsistemas y controladores de memoria.

Especificaciones de AMBA

AMBA es un conjunto de protocolos de interconexión. La última versión AMBA 5 incluye las siguientes especificaciones:

- APB : La última versión de Advanced Peripheral Bus (APB) se introdujo en AMBA 2.0. Este es un protocolo simple sin canalización que se utiliza para la comunicación maestro-esclavo con periféricos de bajo ancho de banda. Se pueden conectar varios periféricos a un bus compartido, que se gestiona a través de un puente (como el puente AXI-APB) o directamente por un maestro (procesador/controlador). En las especificaciones APB, se utiliza el mismo conjunto de señales para leer y escribir en el bus y no se admite ninguna transferencia de datos en ráfaga.

- ASB : Advanced System Bus (ASB) es un protocolo canalizado para mecanismos de comunicación con componentes de alta frecuencia y gran ancho de banda. Admite transferencias en ráfaga y múltiples maestros de bus. Este sistema de bus admite la interconexión entre múltiples maestros y memorias. El bus consta de cuatro tipos de bloques: maestro, árbitro, esclavo y decodificador. En cualquier momento sólo un maestro puede acceder al bus. Un maestro solo puede acceder al bus con la ayuda de un árbitro mientras necesita seleccionar un esclavo para la comunicación mediante un decodificador. El maestro inicia la operación de lectura o escritura y el esclavo seleccionado responde a las solicitudes de lectura y escritura.

-

AHB : El bus avanzado de alto rendimiento (AHB) se introdujo en AMBA 2.0. Es una alternativa al ASB donde se requieren características de alto rendimiento. Admite configuraciones de bus de datos más amplias, transferencia maestra de bus de ciclo único, transacciones divididas y operaciones de reloj único. Al igual que ASB, el bus AHB también requiere componentes adicionales para gestionar los mecanismos de comunicación, como el multiplexor de lectura, el multiplexor de escritura, el decodificador, el árbitro, el multiplexor de dirección y control. El sistema de bus consta de tres señales: señal de dirección, bus de escritura de datos y bus de lectura de datos. La señal de dirección se usa para seleccionar un esclavo, el bus de datos de escritura se usa para mover comandos del maestro al esclavo y el bus de datos de lectura se usa para mover respuestas de los esclavos a los maestros. El maestro accede al bus solicitando al árbitro y utiliza el decodificador para seleccionar un esclavo. El bus se asigna a un maestro según un esquema de priorización. Este esquema está definido en las especificaciones AMBA y difiere entre diferentes diseños. Hay 20 señales AHB diferentes en total, en comparación con las 15 señales en ASB.

- AHB-lite : Es una versión simplificada de AHB. Soporta mecanismos de comunicación con un solo maestro sin necesidad de ningún árbitro. También excluye algunas características de alto rendimiento de AHB, como transacciones divididas y reintentos.

- AXI : Interfaz extensible avanzada (AXI) es una especificación de interconexión punto a punto que supera las limitaciones de los protocolos de bus compartido al conectar múltiples agentes. Fue diseñado específicamente para gestionar mecanismos de comunicación con procesadores y controladores multinúcleo. Las especificaciones AXI se introdujeron en AMBA 3.0. En lugar de utilizar un bus del sistema, utiliza interfaces bien definidas para mecanismos de comunicación de baja latencia y gran ancho de banda. Tiene varias características mejoradas en comparación con AHB, como múltiples transferencias canalizadas, subprocesos de lectura/escritura separados, anchos de bus de datos más amplios y transferencias de datos en ráfagas.

- AXI-lite : Es una versión simplificada del protocolo AXI. Carece de transferencia de datos intermitente en comparación con las especificaciones AXI completas.

- AXI Streaming : Esta es una modificación del protocolo AXI para admitir la transmisión de datos de maestros a esclavos. En este protocolo, los datos sólo se mueven en una dirección, del maestro al esclavo. Los canales de lectura/escritura no están separados en el flujo AXI, a diferencia de la especificación AXI completa. Es posible transferir múltiples flujos de datos entre maestro y esclavo. Este protocolo es útil en aplicaciones como transmisión de video, transmisión de juegos, etc.

- ACE : Las especificaciones AXI Coherency Extensions (ACE) se introdujeron en AMBA 4.0. Esta especificación se utiliza para gestionar mecanismos de comunicación en procesadores/controladores multinúcleo con memorias caché coherentes compartidas entre ellos. La especificación ACE amplía los canales de lectura y escritura de AXI mediante el uso de direcciones de snoop, canales de datos de snoop y canales de respuesta de snoop separados. Estos canales adicionales implementan un protocolo de coherencia basado en escuchas ilegales.

- ACE-lite : ACE-lite es una versión simplificada de la especificación ACE completa. Está diseñado para gestionar mecanismos de comunicación con agentes que no tienen su propia memoria caché, pero que aún pueden participar en un sistema de coherencia compartible utilizando coherencia unidireccional. Ejemplos de tales agentes son los controladores DMA y los bloques Network-on-Chip.

- CHI : Coherent Hub Interface (CHI) es una reelaboración del protocolo ACE para sistemas informáticos heterogéneos y complejos. El protocolo ACE utiliza una interconexión de comunicación maestro-esclavo a nivel de señal utilizando una gran cantidad de cables y canales adicionales para escuchas y respuestas. Esto funciona bien para pequeños grupos coherentes, como los SoC móviles de doble o cuatro núcleos. Sin embargo, con muchos componentes heterogéneos como DSP, GPU, NPU, etc., AXI tiene limitaciones ya que sigue siendo un protocolo basado en señales. CHI es un rediseño del bus AXI que utiliza protocolos de interfaz basados en paquetes en lugar de un sistema de bus basado en señales.

Conclusión

Si trabaja en diseño VLSI, probablemente haya oído hablar o haya aprendido sobre los protocolos AMBA. AMBA ha evolucionado a lo largo de los años para satisfacer las necesidades de los diseños de SoC de próxima generación y los futuros desarrollos de circuitos integrados. Los protocolos AMBA son un estándar abierto y se pueden descargar desde el sitio web de Arm después de un registro gratuito. Este artículo proporciona una descripción general de varias especificaciones AMBA. Puede descargar las especificaciones del sitio web de Arm y obtener más información sobre estos protocolos de diseño de chips.