En el tutorial anterior , cubrimos cómo conectar un módulo GPS NEO-6M con Raspberry Pi (RPi). El módulo se comunica con RPi a través del receptor/transmisor asíncrono universal o el protocolo UART .

UART es el protocolo de comunicación de datos punto a punto más común. Pero no es el único protocolo de comunicación serie. En la electrónica integrada, los protocolos I2C y SPI también se utilizan ampliamente para la comunicación de datos en serie. A diferencia de UART, I2C y SPI son estándares de datos en serie síncronos maestro-esclavo.

En este tutorial, discutiremos los conceptos básicos del protocolo I2C.

¿Qué es un I2C?

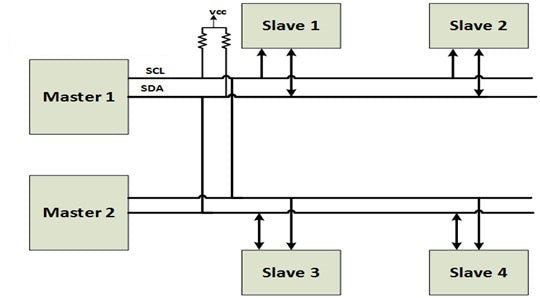

Un circuito interintegrado (I2C) o interfaz de dos hilos (TWI) es un protocolo serie síncrono desarrollado originalmente por Philips Semiconductors (ahora NXP). Es un bus serie multimaestro y multiesclavo para dispositivos de baja velocidad que requiere solo dos cables para la comunicación de datos en serie entre múltiples dispositivos. Se puede implementar fácilmente con dos canales de entrada/salida digitales en un solo dispositivo.

Un bus I2C tiene sólo dos cables a través de los cuales cientos de dispositivos pueden comunicar datos en serie.

Como estándar de comunicación maestro-esclavo, al menos un dispositivo conectado al bus debe ser el maestro. Es el dispositivo maestro el que genera una señal de reloj para la comunicación serie síncrona.

Los dispositivos esclavos pueden transferir datos hacia y desde los dispositivos maestros, que acceden a los dispositivos esclavos a través de sus direcciones I2C. La dirección de cada dispositivo esclavo en un bus I2C debe ser única. Sin embargo, los dispositivos esclavos I2C aún deben obtener sus direcciones de NXP.

Solo hay dos cables en I2C donde se pueden conectar dispositivos:

1. Datos serie (SDA): la línea a través de la cual los dispositivos maestro y esclavo comunican datos serie

2. Reloj serie (SCK): la línea a través de la cual los dispositivos maestros generan la señal de reloj.

I2C es un tipo de comunicación semidúplex. Nota: Un dispositivo maestro solo puede leer o escribir datos en el esclavo a la vez. Además, la señal de reloj y las operaciones de lectura y escritura están controladas por los dispositivos maestros.

Si bien puede haber una cantidad ilimitada de dispositivos maestros conectados al bus I2C, la cantidad máxima de dispositivos esclavos puede ser 112 (en direccionamiento de 7 bits) o 1008 (en direccionamiento de 10 bits).

Los controladores de bus I2C son de drenaje abierto, lo que significa que los dispositivos pueden tirar de la línea de señal I2C hacia abajo, pero no hacia arriba. De forma predeterminada, ambas líneas se elevan mediante resistencias pull-up hasta que un dispositivo maestro accede al bus. Esto es útil para evitar la contención del autobús.

Debido a que los dispositivos maestros solo pueden bajar la línea de señal, no puede haber conflicto entre múltiples maestros, como cuando un maestro baja la línea mientras que el otro la eleva. Si en algún momento la línea de señal es baja, significa que está accediendo a un dispositivo maestro.

Por lo tanto, sólo un maestro puede acceder al bus I2C a la vez. Y el bus maestro sólo puede leer o escribir datos con un esclavo a la vez.

Los datos en serie comunicados por I2C se dividen en paquetes de datos de 8 bits. La velocidad de transferencia de datos depende de la frecuencia del reloj. En el modo predeterminado, la frecuencia del reloj es de 100 a 400 kHz.

La frecuencia del reloj es:

- 1 MHz en modo rápido I2C

- 3,4 MHz en modo de alta velocidad

- 5 MHz en modo ultrarrápido

Ventajas de un I2C

UART es la interfaz serie más común, pero tiene desventajas. Cuando se utiliza UART, la comunicación de datos solo es posible entre dos dispositivos. Estos dispositivos también deben aceptar un protocolo común y tener casi la misma velocidad de reloj.

Es posible conectar más de dos dispositivos a líneas UART, pero esto conlleva un alto riesgo de contención en el bus. En la práctica, la velocidad de datos máxima que se puede lograr con UART es de 230.400 bps. Y en cada transmisión de datos de 8 bits, hay una sobrecarga de 2 bits.

Tampoco es fácil implementar UART en software. La comunicación UART viable requiere un chip UART externo o integrado.

Por otro lado, una interfaz periférica en serie (SPI) permite solo un dispositivo maestro pero múltiples dispositivos esclavos. Para conectar un dispositivo esclavo, se requieren cuatro líneas. Para cada dispositivo esclavo, se requiere una línea adicional para la selección del chip. Por lo tanto, a pesar de la alta velocidad de datos (hasta 10 Mbps) y la comunicación full-duplex, no es práctico conectar varios dispositivos esclavos a través de un SPI debido a las líneas adicionales necesarias para cada esclavo. Esta limitación es más evidente cuando todo el circuito está dispuesto en una PCB.

Por lo general, un SPI solo es bueno para la comunicación de datos full-duplex de alta velocidad desde un dispositivo maestro (como un microcontrolador o una computadora integrada) con un número limitado de periféricos esclavos (digamos, dos o tres). Sin embargo, un SPI es una alternativa a UART para la comunicación de datos full-duplex de alta velocidad con más de un dispositivo periférico.

Básicamente, un I2C representa lo mejor de UART y SPI. Aunque permite la comunicación semidúplex, utilizando I2C, un número ilimitado de dispositivos maestros pueden comunicar datos en serie con cientos de dispositivos esclavos a través de solo dos cables.

Dado que los dispositivos maestros sólo pueden conducir líneas bajas, la contención del bus no es una preocupación. Las velocidades de datos se encuentran entre las de UART y SPI (hasta 5 Mbps) y hay una sobrecarga de solo 1 bit (ACK/NACK) por cada byte transmitido a través del protocolo I2C.

Un I2C todavía requiere hardware complejo en comparación con un SPI, pero no es tan complejo como UART. Además, la implementación de software de un I2C es bastante factible.

Además, un I2C es particularmente útil cuando se requiere comunicación de datos de baja velocidad con múltiples dispositivos o por múltiples maestros a través de solo dos cables. Es por eso que se usa comúnmente en sensores y módulos integrados. Al usar un I2C, un microcontrolador (como Arduino) o una computadora integrada (como Raspberry Pi) pueden conectarse y comunicarse con cientos de sensores a través de solo dos cables, mientras solo conectan sus dos canales/pines.

Desventajas de un I2C

Un I2C permite la comunicación de datos en serie con múltiples dispositivos y múltiples maestros usando solo dos cables, pero tiene bajas tasas de transferencia de datos y carece de capacidades full-duplex. I2C simplemente no es una opción cuando se requiere comunicación full-duplex o cuando se requieren altas velocidades de datos.

Eso significa:

- UART es bueno para la comunicación básica full-duplex entre dos dispositivos con velocidades de reloj similares.

- Un SPI es bueno para la comunicación de datos full-duplex y de alta velocidad con dos o más periféricos.

- Un I2C es bueno para la comunicación de datos a baja velocidad con múltiples dispositivos, entre múltiples maestros en un bus de 2 cables.

El hardware I2C

La implementación de un I2C requiere dos controladores de salida de drenaje abierto (colector abierto en terminología TTL). Ambos cables en un bus I2C deben desconectarse con una resistencia adecuada. Los canales I2C en la mayoría de los sensores y módulos comunican con éxito datos en serie a través de dos o tres metros de cable.

Para la transmisión de datos a largas distancias, se requieren tarjetas de conexión I2C dedicadas.

La mayoría de los microcontroladores y computadoras integradas tienen hardware I2C dedicado, que puede funcionar como maestro I2C y esclavo I2C. Como esclavo I2C significa que también tienen una dirección I2C. Con el hardware I2C, pueden generar condiciones de inicio y parada, recibir una dirección I2C y enviar y recibir datos en serie a través del protocolo.

Si la dirección I2C se implementa mediante software, los bits de datos deben muestrearse al menos dos veces por ciclo de reloj. La mayoría de los microcontroladores tienen suficiente frecuencia de reloj para poder muestrear fácilmente datos I2C utilizando un temporizador/contador interno con o sin preescalador.

Niveles de voltaje I2C

Los voltajes típicos utilizados para I2C son +5 y +3,3V. Sin embargo, I2C es flexible y también puede mantener la comunicación de datos con dispositivos/interfaces con otros niveles de voltaje.

Al conectar un dispositivo de mayor voltaje a un dispositivo de menor voltaje a través de I2C, se requiere precaución. A veces es suficiente llevar el bus I2C a un nivel de dispositivo de voltaje más bajo. Pero todavía existe la posibilidad de que el dispositivo de mayor voltaje dañe el dispositivo de menor voltaje. Se recomienda conectar los dos dispositivos con diferentes niveles de voltaje en el bus I2C utilizando una placa de cambio de nivel I2C adecuada.

direcciones I2C

Los dispositivos maestros en un bus I2C no necesitan tener una dirección, ya que generan la señal de reloj en una línea SCL. Los dispositivos esclavos deben tener direcciones únicas en un bus I2C.

Las direcciones I2C de los dispositivos esclavos pueden ser de 7 o 10 bits. Algunos de estos dispositivos tienen direcciones fijas, mientras que otros tienen líneas de dirección que se pueden conectar para configurar la dirección del dispositivo a través de una interfaz I2C.

Dado que hay un número limitado de direcciones I2C (solo 112 direcciones en 7 bits y 1008 direcciones en 10 bits), existe la posibilidad de que dos dispositivos I2C tengan la misma. Se puede conectar más de un dispositivo I2C con la misma dirección a un controlador/computadora mediante un concentrador I2C.

El protocolo I2C

De forma predeterminada, ambas líneas I2C (SDA y SCL) están en nivel alto. Puede haber uno o más dispositivos maestros conectados a un bus I2C. La comunicación de datos la inicia un dispositivo maestro.

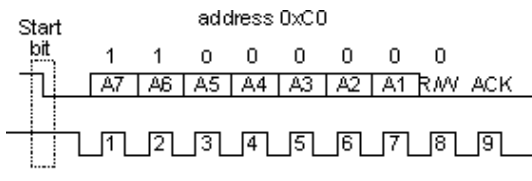

Un dispositivo maestro genera una condición inicial seguida de la dirección del dispositivo esclavo. La dirección del dispositivo esclavo debe ser única. En el direccionamiento de 7 bits, el bit 0 del byte de dirección indica si el maestro lee o escribe en el esclavo I2C. Si el bit 0 del byte de dirección es 0, el dispositivo maestro escribe datos en el esclavo I2C. Si es 1, el dispositivo maestro lee datos del esclavo I2C.

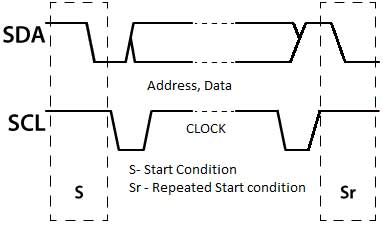

Después de seleccionar un dispositivo esclavo, se transfieren tramas de datos compuestas por datos de 8 bits y bits de confirmación entre el maestro y el esclavo. Puede haber condiciones de inicialización repetidas para que un maestro lea y escriba datos en serie con uno o más esclavos I2C.

Una vez que se completa la comunicación de datos, el dispositivo maestro debe generar una condición de parada para finalizar la comunicación a través del bus I2C.

El bus I2C también puede ser utilizado por otros dispositivos maestros. De hecho, puede haber una cantidad ilimitada de dispositivos maestros conectados a un bus I2C siempre que la capacitancia del bus no supere los 400 pF.

![]()

![]()

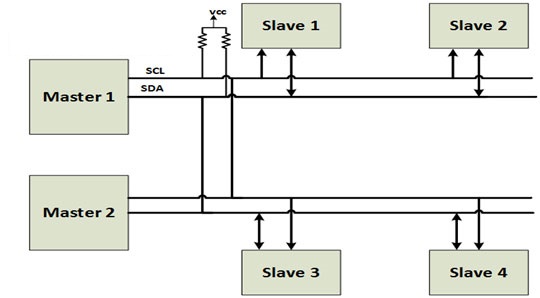

La condición inicial

Para generar la condición inicial, un dispositivo maestro necesita bajar un SDA mientras deja el SCL alto.

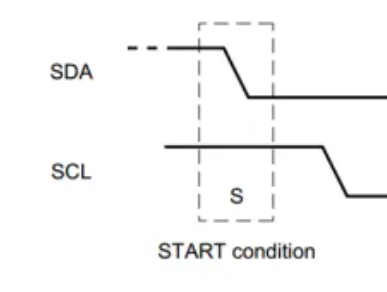

Si dos dispositivos maestros intentan acceder a I2C al mismo tiempo, el que baje primero el SDA obtendrá la propiedad del bus. Esto se llama arbitraje.

Cuando hay una transición de alto a bajo en una línea SDA, los esclavos I2C reciben una alerta de que una transmisión está a punto de comenzar. Una vez que el bus es controlado por un maestro, puede leer y escribir datos en uno o más dispositivos esclavos, generando condiciones de inicio repetidas.

Hasta que el bus maestro actual genere la condición de parada, otros dispositivos maestros no pueden obtener el control del bus I2C.

Marcos de direcciones

Los datos se comunican a través del bus I2C en tramas de 8 bits (paquetes de datos). El primer cuadro después de la condición inicial es siempre un cuadro de dirección. Esta trama identifica el dispositivo esclavo con el que debe comunicarse el maestro del bus I2C.

En esta trama, el maestro transmite la dirección de 7 bits de un dispositivo esclavo, comenzando desde el MSB de la dirección I2C. Le sigue un bit R/W, que determina si el maestro leerá o escribirá datos en el esclavo. Si el bit R/W es 0, el dispositivo maestro escribe datos en el esclavo I2C. Si es 1, el dispositivo maestro lee datos del esclavo I2C.

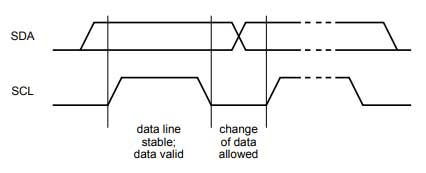

Después de la condición de inicio, el maestro del bus debe bajar la línea SCL. Los bits se muestrean cada vez que la línea SCL sube. Los datos (bits) en la línea SDA deben permanecer estables cuando el SCL es alto; de lo contrario, se interpretará como una condición de inicio o parada repetida. Los bits de datos sólo pueden cambiar cuando el SCL es bajo. Después de la condición inicial, el maestro baja el SCL y los datos se colocan en la línea SDA. Después de eso, el esclavo muestrea los datos en cada transición de bajo a alto de la señal SCL.

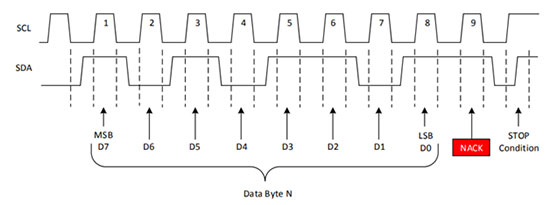

Cada trama de datos de 8 bits termina con un bit ACK/NACK. Después de la transferencia de 8 bits, el dispositivo receptor obtiene el control de la línea SDA. Si el dispositivo receptor baja la línea SDA antes del noveno pulso de reloj, significa que ha recibido con éxito la trama de datos de 8 bits.

Si esto no ocurre, significa que no se pudo recibir la trama de datos o que los datos no se pudieron analizar según el protocolo I2C. En este caso, el dispositivo receptor no baja la línea SDA, sino que corresponde al maestro terminar la comunicación de datos generando una condición de parada o una condición de inicio repetida.

En el caso de una trama de direcciones, el dispositivo receptor es siempre un dispositivo esclavo.

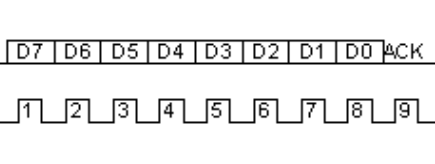

marcos de datos

Después de enviar una trama de dirección, el bus maestro continuará enviando pulsos de reloj. Dependiendo del bit R/W, el dispositivo maestro lee o escribe los datos. Después de cada trama de 8 bits, el dispositivo receptor baja la línea SDA en el noveno pulso de reloj.

Puede haber cualquier cantidad de tramas de datos intercambiadas entre un maestro y un esclavo, después de que el maestro selecciona un esclavo y la operación de lectura/escritura envía la señal de inicio y luego una trama de dirección.

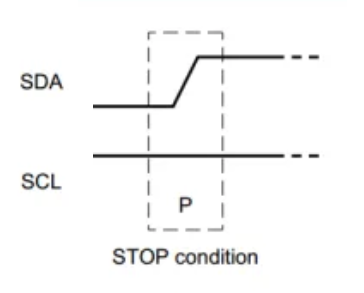

La condición de parada

La condición de parada

Una vez que un maestro obtiene el control del bus I2C, puede leer/escribir datos en serie con cualquier número de esclavos, generando condiciones de arranque repetidas.

Para liberar el bus, el maestro debe generar una condición de parada. La condición de parada se genera tirando de la línea SDA de mayor a menor mientras la línea SCL está alta.

Esta es la razón por la que los bits de datos nunca deberían cambiar cuando el pulso de reloj en la línea SCL es alto. De lo contrario, se interpretará como una condición de parada falsa o un inicio en falso repetido.

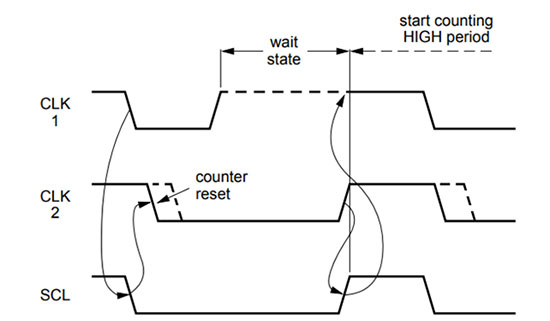

Ver estiramientos

Si un dispositivo esclavo no está listo o no puede procesar los datos recibidos, puede bajar la línea SCL para indicar que necesita tiempo para recibir/procesar los datos. Cuando el dispositivo está listo, puede configurar la línea SCL en alto, lo que indica que el maestro puede reiniciar la comunicación en serie. Esto se llama alargamiento del reloj.

Los bits de datos siempre se muestrean en una transición de bajo a alto del pulso de reloj en una línea SCL. Los dispositivos esclavos solo pueden bajar la línea SCL después de que el maestro libera el bus I2C. Cuando un dispositivo esclavo baja la línea SCL, los dispositivos maestros en el bus I2C evitan generar pulsos de reloj o colocar datos en una línea SDA hasta que el esclavo borre la línea SCL.

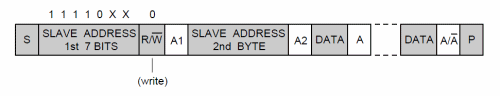

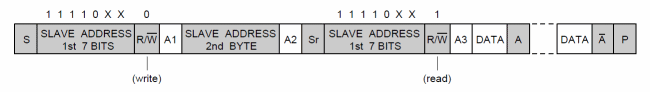

Direccionamiento I2C de 10 bits

Los dispositivos I2C avanzados tienen direcciones de 10 bits. Se pueden utilizar con dispositivos de direcciones de 7 bits, ya que el marco de direcciones para dispositivos de 10 bits siempre comienza con la secuencia de 5 bits, 11110.

Esta cadena indica una dirección de 10 bits del dispositivo maestro. Para seleccionar un esclavo I2C con una dirección de 10 bits, el dispositivo maestro debe enviar dos tramas de direcciones para escribir datos en el esclavo, o tres tramas de direcciones para leer datos del esclavo.

Cuando el maestro necesita escribir datos en un esclavo de dirección de 10 bits, debe enviar dos tramas de dirección. La primera trama de dirección contiene la secuencia de 5 bits 11110, seguida de dos bits de dirección esclava y el bit R/W. El bit R/W debe ser 0 en este caso.

Después de enviar la primera trama, debe esperar el ACK en el noveno pulso de reloj. Si el maestro detecta exitosamente el bit de reconocimiento (una línea SCL bajada por el dispositivo receptor), envía los 8 bits restantes de la dirección del esclavo en la siguiente trama.

Cuando un maestro necesita leer datos de un esclavo de dirección de 10 bits, el bit R/W en el primer marco de dirección sigue siendo 0, pero al segundo marco de dirección le sigue una condición de inicio repetida.

Después de repetir la condición de inicio, la primera trama de dirección se envía de vuelta al esclavo con el bit R/W establecido en 1.

Protocolo I2C avanzado

La mayoría de los dispositivos I2C tienen direcciones de 7 bits y utilizan el modo estándar donde la velocidad de transferencia de datos es de 100 Kbps. Los dispositivos I2C avanzados funcionan en modo rápido, de alta velocidad o ultrarrápido y normalmente tienen direcciones de 10 bits.

Los dispositivos I2C de modo rápido son compatibles con versiones anteriores y también pueden funcionar con controladores I2C más lentos. Los dispositivos I2C de alta velocidad utilizan dos estados de reloj, SCLH y SCLL, y tienen circuitos de supresión de sobretensiones en ambas líneas del bus I2C.

Los dispositivos de alta velocidad no utilizan estiramiento o arbitraje de reloj porque tienen controladores de salida de línea mejorados.

En el próximo tutorial, analizaremos la comunicación serie síncrona cuando se utiliza el protocolo I2C en Raspberry Pi.