En los tutoriales anteriores, todos los circuitos diseñados fueron circuitos combinacionales . En circuitos combinacionales, la salida binaria depende únicamente del estado actual de las entradas. Entonces, en realidad, los circuitos combinacionales tienen operación estática. Pueden tener entrada de un conjunto fijo de valores para los cuales la salida resulta en un intervalo definido en cualquier instante de tiempo.

En la práctica, la mayoría de los dispositivos electrónicos tienen funcionamiento dinámico. Procesan un conjunto de información binaria recibida dentro de un intervalo de tiempo en diferentes instantes para producir de manera efectiva un resultado relevante en tiempo real. Para lograr esto, los dispositivos electrónicos contienen elementos de memoria para almacenar información digital recibida en un instante anterior y tienen circuitos digitales que pueden procesar información recibida tanto en el instante presente como en el instante anterior para producir un resultado relevante. Por ejemplo, es posible que una computadora necesite mantener alineados los resultados de un cálculo anterior para un cálculo siguiente.

Así, el tipo de circuito digital cuya salida depende no sólo del estado actual sino también del estado anterior de las entradas se denomina circuito secuencial. Los circuitos secuenciales son circuitos combinacionales con retroalimentación de elementos de memoria. En cualquier instante, el circuito combinacional dentro de un circuito secuencial recibe la entrada actual y recupera los estados de entrada anteriores de los elementos de memoria para realizar el cálculo. Una vez que se completa el cálculo, antes de que ocurra el siguiente cálculo, la parte combinacional del circuito secuencial almacena los estados de entrada recibidos actualmente en elementos de memoria. Se puede decir que los elementos de memoria en un circuito secuencial funcionan como un elemento de retroalimentación. Con elementos de memoria a su disposición, los circuitos secuenciales pueden almacenar, retener y recuperar el estado anterior de las entradas o, por ejemplo, los estados de las entradas en el instante anterior.

Hay dos tipos de circuitos secuenciales:

1 ) Circuitos secuenciales síncronos

2 ) Circuitos secuenciales asíncronos

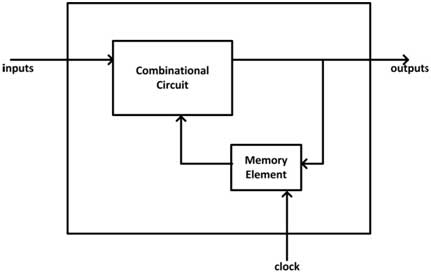

Los dos tipos de circuitos secuenciales difieren en el esquema de temporización de sus señales. Los circuitos secuenciales síncronos operan con datos en señales de reloj periódicas, por lo tanto, operan con datos binarios en instantes de tiempo discretos. La señal del reloj periódico es generada por un dispositivo de sincronización llamado generador de reloj y la señal del reloj se genera y recibe como pulsos. El cálculo de datos mediante el circuito combinacional del circuito secuencial síncrono, así como el almacenamiento y recuperación de datos de los elementos de la memoria, se lleva a cabo cuando llegan los pulsos del reloj, es decir, cuando la señal del reloj cambia de 0 a 1 en dichos circuitos. . Mientras tanto, la señal de reloj vuelve a 0, el circuito combinacional del circuito síncrono se prepara para el siguiente ciclo de cómputo mientras que los elementos de memoria almacenan el estado anterior de las entradas y se preparan para que el mismo sea recuperado a la llegada del siguiente pulso. Para el funcionamiento sincrónico de circuitos combinacionales y elementos de memoria según la señal de reloj periódica, se controla correspondientemente el retardo de propagación en las puertas lógicas que construyen los respectivos circuitos. La velocidad a la que el reloj maestro genera los pulsos debe ser lo suficientemente lenta como para permitir que responda el circuito más lento. Esto limita la velocidad de todos los circuitos. Se puede decir que los circuitos síncronos se construyen integrando circuitos combinacionales, elementos de memoria y un generador de reloj. Un circuito secuencial síncrono se puede representar mediante el siguiente diagrama de bloques:

Fig. 1: Diagrama de bloques de circuitos secuenciales síncronos

En los circuitos secuenciales asíncronos, la retroalimentación de los estados de entrada anteriores al circuito combinacional puede ocurrir en cualquier instante, en lugar de ser de naturaleza periódica y, por lo tanto, depende del orden de las señales de entrada en lugar de la aparición de cualquier pulso de reloj. En estos circuitos, los elementos de memoria están acoplados a circuitos de retardo de tiempo de modo que se pueda recibir retroalimentación sobre el estado anterior de las entradas en el instante en que se reciben las entradas actuales. En la mayoría de los casos, el retardo de propagación a través de las puertas de los elementos de memoria es suficiente para producir el retardo de tiempo requerido. En estos circuitos, la capacidad de almacenamiento de los elementos de memoria también depende del retardo de propagación de la señal. Los circuitos asíncronos pueden ser inestables o poco confiables en ocasiones debido a retrasos sin precedentes en los circuitos o en las entradas del circuito. Por tanto, el diseño de circuitos secuenciales asíncronos siempre requiere precaución y detalles técnicos adicionales. Así, se puede decir que los circuitos secuenciales asíncronos se construyen integrando circuitos combinacionales y elementos de memoria con retardos de tiempo definidos en la propagación de la señal.

En comparación con los circuitos combinacionales, los circuitos secuenciales son más lentos ya que necesitan sincronizarse según la señal del reloj en el caso de circuitos síncronos o deben tener retardos de tiempo definidos en el caso de circuitos asíncronos. Los circuitos combinacionales, al depender únicamente de los estados de entrada actuales , procesan los datos inmediatamente afectados únicamente por el retardo de propagación de las señales a través de las puertas.

Sin embargo, los circuitos secuenciales incorporan elementos de memoria que son una parte vital de cualquier electrónica moderna. La mayoría de los dispositivos electrónicos necesitan almacenar o retener datos según sea necesario para el cálculo. Los circuitos secuenciales, aunque tienen una velocidad limitada en su propio concepto de diseño, son los circuitos digitales más abundantes en electrónica.

Elementos de la memoria –

Los elementos de la memoria son esenciales en la construcción de cualquier circuito secuencial. El elemento de memoria más simple puede almacenar un solo bit en cualquier momento. Un grupo de estos elementos de la memoria forma recuerdos más grandes. Hay dos tipos de elementos de memoria de almacenamiento de un solo bit: Latches y Flip-Flops. Ambos pueden almacenar un bit a la vez.

Los pestillos son elementos de memoria sensibles al nivel que responden al estado 0 o 1 de la señal, mientras que los flip-flops son elementos de memoria sensibles a la transición que responden a la transición de la señal de 0 a 1 y viceversa. Los flip-flops, que responden a las transiciones de señales, se denominan dispositivos sensibles a los bordes. Las propias chanclas están construidas con pestillos. Los pestillos se utilizan como elementos de memoria en circuitos secuenciales asíncronos, pero no se pueden utilizar en circuitos síncronos. En los circuitos síncronos, los flip-flops se utilizan como elementos de memoria.

En estado estable, la salida de un flip-flop permanece 1 o 0. La salida de un flip-flop cambia sólo cuando recibe un pulso de reloj. La salida de un flip-flop depende de la entrada de datos actual o del valor actualmente almacenado en él o de ambos. El circuito combinacional de un circuito síncrono debe sincronizarse con los pulsos de reloj y alcanzar un estado estable antes de que los estados de entrada anteriores pasen a ser almacenados en los flip-flops. El circuito debe poder responder al cambio de estado de los flip-flops antes de que llegue el siguiente pulso de reloj. Por lo tanto, la duración del pulso de reloj debe estar predeterminada para el correcto funcionamiento de un circuito síncrono. Cabe señalar que estos elementos de memoria (latches y flip-flops) retienen información binaria hasta que reciben energía. Si hay un corte de energía, los datos que conservan en ese momento se pierden.

Cerraduras -

Los pestillos son dispositivos de memoria sensibles al nivel. Se utilizan en circuitos secuenciales asíncronos. También son los componentes básicos de las chanclas. Hay tres tipos de cerraduras:

1 ) Bloqueo SR

2 ) Bloqueo S'R'

3 ) Bloqueo D

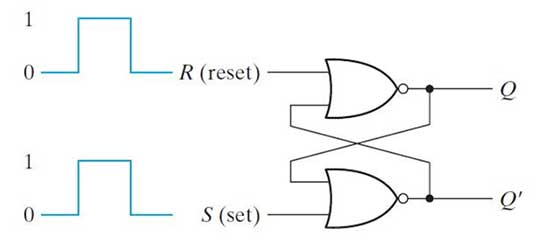

SR Latch : el pestillo SR está construido por dos puertas NOR acopladas cruzadas. Tiene dos entradas: configurar (S) y restablecer (R), mientras que dos salidas Q y Q'. OQ y Q' normalmente son complementarios entre sí. Cuando el conjunto de entrada es 1 y el restablecimiento de entrada es 0, la salida Q se convierte en 1 y Q' se convierte en 0. Cuando el conjunto de entrada es 0 y el restablecimiento de entrada es 1, la salida Q se convierte en 0 y Q' se convierte en 1. Cuando ambos set y reset son 0, el flip-flop SR retiene el estado de salida, es decir, si previamente Q se volvió 1 y Q' se volvió 0, se retendrán los mismos estados mientras set y reset sean 0. Del mismo modo, si previamente Q se volvió 0 y Q' se convirtió en 1, se mantendrán los mismos estados siempre que tanto set como reset sean 0. Si set y reset son 1, entonces Q y Q' se convierten en 0, lo cual está prohibido. Por lo tanto, ya sea que se establezca o se restablezca en 1, se cambia el bit almacenado por el pestillo SR; si ambos se vuelven 0, el bit almacenado se mantiene mientras que ambos estén en 1 es una condición prohibida. La cerradura SR se puede construir con puertas NOR de la siguiente manera:

Fig. 2: Diagrama de puerta lógica del pestillo SR

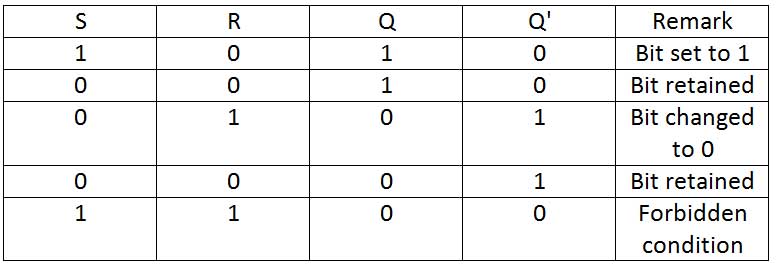

El funcionamiento de una cerradura SR se puede resumir en la siguiente tabla de funciones:

Fig. 3: Tabla de verdad del bloqueo SR

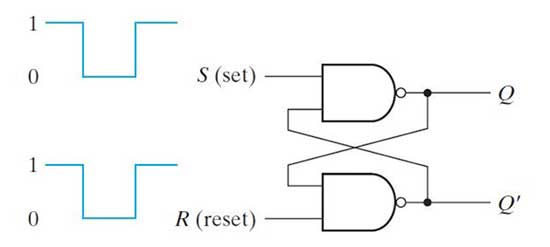

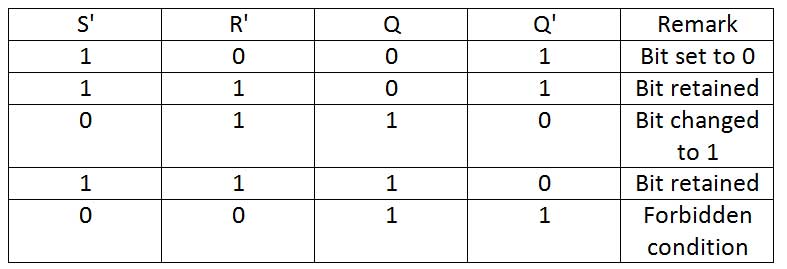

Pestillo S'R' : el pestillo S'R' es un tipo de pestillo SR construido a partir de dos puertas NAND acopladas en lugar de dos puertas NOR acopladas. En el bloqueo S'R', cuando el conjunto de entrada es 1 y el restablecimiento de entrada es 0, la salida Q se convierte en 0 y Q' se convierte en 1. Cuando el conjunto de entrada es 0 y el restablecimiento de entrada es 1, la salida Q se convierte en 1 y Q' se convierte en 0. Cuando set y reset son 1, el flip-flop S'R' retiene el estado de salida, es decir, si anteriormente Q se había convertido en 0 y Q' se había convertido en 1, se conservarán los mismos estados siempre que set y reset sean 1. Del mismo modo, si anteriormente Q se había convertido en 1 y Q' se había convertido en 0, se mantendrán los mismos estados siempre que tanto set como reset sean 1. Si set y reset son 0, entonces tanto Q como Q' se convertirán en 1, lo cual. esta prohibido. Por lo tanto, si el valor establecido o restablecido es 0, se cambiará el bit almacenado por el pestillo S'R'; si ambos se vuelven 1, el bit almacenado se retendrá, mientras que ambos se vuelven 0 es una condición prohibida. Se puede ver que la salida del pestillo S'R' es siempre un complemento a la salida del pestillo SR, razón por la cual recibió su nombre: pestillo S'R'. El pestillo S'R' se puede construir mediante puertas NAND de la siguiente manera:

Fig. 4: Diagrama de puerta lógica de bloqueo S'R'

El funcionamiento de una cerradura S'R' se puede resumir en la siguiente tabla de funciones:

Fig. 5: Tabla de verdad del bloqueo S'R'

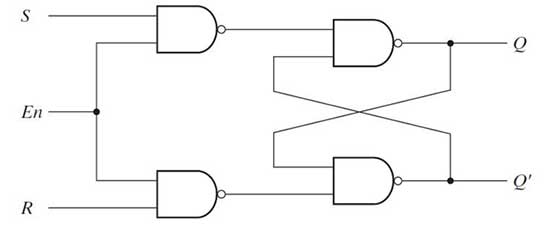

El pestillo SR o S'R' puede tener una entrada de habilitación adicional para controlar el cambio en su estado. La entrada de habilitación se puede agregar conectando dos puertas NAND adicionales al circuito de bloqueo SR básico de la siguiente manera:

Fig. 6: Diagrama de puerta lógica de bloqueo SR con entrada de habilitación

La cerradura SR con entrada de habilitación tiene la siguiente tabla de funciones:

Fig. 7: Tabla de verdad de la cerradura SR con entrada de habilitación

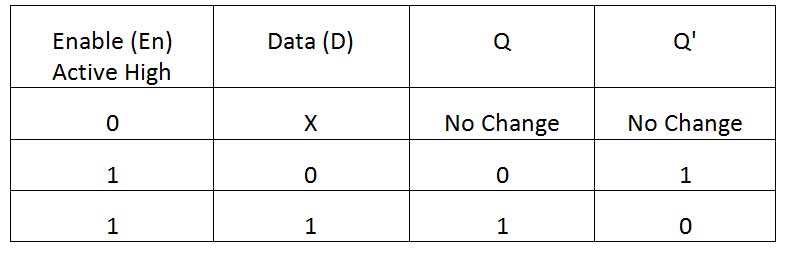

D Latch : D Latch es una variante del pestillo SR o pestillo S'R' para eliminar la condición prohibida de su tabla de funciones. En un D Latch, solo hay dos entradas: Datos (D) y Habilitar (En) y hay dos salidas Q y Q'. La entrada de habilitación puede ser activa baja o activa alta. Si la entrada de habilitación está activa en nivel alto, si hay 0 en la entrada de habilitación, el pestillo retendrá los datos y no se transferirán a las salidas. Cuando la entrada de habilitación se establece en 1, si los datos de entrada son 0, Q se convierte en 0 y Q' se convierte en 1, mientras que si los datos de entrada son 1, Q se convierte en 1 y Q' se convierte en 0. Para una entrada de habilitación alta activa, bloquee D tiene la siguiente tabla de funciones –

Fig. 8: Tabla de verdad del cierre D alto activo

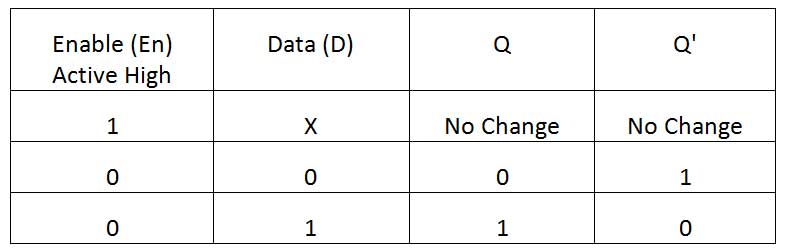

Si la entrada de habilitación está activa en nivel bajo, el pestillo retendrá los datos cuando la entrada de habilitación esté configurada en 1 y se transferirán a la salida cuando la entrada de habilitación esté configurada en 0. La entrada de habilitación se puede activar en un nivel bajo conectando un puerto del inversor. Con la entrada de habilitación baja activa, el D Latch tiene la siguiente tabla de funciones:

Fig. 9: Tabla de verdad del pestillo activo de baja D

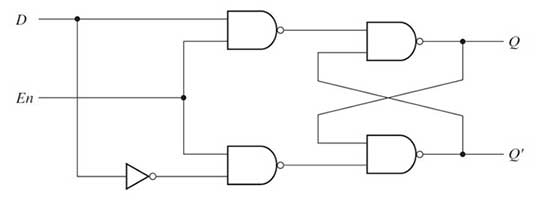

AD El pestillo se construye acoplando la entrada a las puertas NAND en un pestillo SR con entrada Habilitar. Al acoplar las puertas NAND en el primer nivel de implementación de puerta lógica del pestillo D, la entrada de datos se conecta directamente a la entrada Set (S) del pestillo SR mientras se conecta a través de un inversor a la entrada Reset (R) del Pestillo SR. De esta manera, cuando Data (D) es 0, Set es 0 y Reset es 1, mientras que cuando D es 1, Set es 1 y Reset es 0. El pestillo AD tiene el siguiente diagrama de puerta lógica:

Fig. 10: Diagrama del circuito de bloqueo D

Al igual que en un pestillo D, los datos se transfieren a la salida Q cuando Habilitar (En) se establece en 1 en caso de activación alta o en 0 en caso de configuración activa baja mientras se mantiene en el estado inverso de la entrada de habilitación. el candado D también se llama candado transparente.

Los pestillos se utilizan como elementos de memoria en circuitos secuenciales asíncronos. En el próximo tutorial, se analizarán los flip-flops y sus diferentes tipos. Los flip-flops son los elementos de memoria utilizados en circuitos secuenciales síncronos.