Los tutoriales anteriores sentaron las bases para la síntesis lógica y el diseño de circuitos digitales. Los circuitos digitales en general siempre tienen aplicación como dispositivos informáticos, ya sea como procesador, controlador o circuitos integrados para aplicaciones específicas. Como dispositivo informático, el circuito digital de un procesador, controlador o ASIC debe ser esencialmente capaz de realizar operaciones aritméticas. La implementación de operaciones aritméticas mediante circuitos digitales se utiliza además para construir funciones matemáticas y lógica informática compleja.

En un procesador/controlador/ASIC, las operaciones aritméticas con números enteros binarios las realiza la unidad aritmética lógica (ALU), mientras que las operaciones aritméticas con números de coma flotante las realiza la unidad de coma flotante (FPU). La propia unidad de coma flotante está construida a partir de varias ALU. Dentro de una Unidad Central de Procesamiento (CPU) o Unidad de Procesamiento de Gráficos (GPU) de una computadora/dispositivo informático, hay muchas ALU y/o FPU (donde las FPU mismas están construidas a partir de múltiples ALU).

Los circuitos digitales pueden ser de dos tipos: 1) circuitos lógicos combinacionales o 2) circuitos lógicos secuenciales. En un circuito combinacional, la salida del circuito depende únicamente de los valores de entrada en ese momento. En circuitos secuenciales, la salida depende no sólo de la entrada actual sino también de los valores de salida anteriores. Las ALU se construyen utilizando circuitos combinacionales. La ALU suele estar diseñada para realizar las siguientes operaciones:

1) Operaciones aritméticas : generalmente, las operaciones aritméticas admitidas por la ALU son suma, suma con acarreo, resta, resta con préstamo, complemento a dos, incremento, decremento y pase.

2) Operaciones lógicas bit a bit : las operaciones lógicas admitidas por la ALU son AND, OR, OR exclusivo y complemento a uno.

3) Operaciones de desplazamiento de bits : las operaciones de desplazamiento de bits implementadas en una ALU incluyen desplazamiento aritmético, desplazamiento lógico, rotación y rotación mediante transporte.

Por lo tanto, la ALU puede realizar operaciones aritméticas como suma y resta y, por lo tanto, multiplicación y división de números enteros binarios. Un número binario puede estar disponible para la ALU de un procesador digital como una entrada paralela de 8, 16, 32 o 64 bits, dependiendo de si es de 8, 16 o 32 bits. , o 64 bits. procesador de bits. Los componentes básicos de la ALU son los sumadores. Los circuitos de suma se construyen mediante puertas lógicas y flip-flops. Los circuitos sumadores de semiconductores pueden realizar la suma en un tiempo de menos de 1 microsegundo.

Aprendamos sobre varios circuitos combinacionales: medio sumador, sumador completo, medio restador, restador completo, sumador paralelo de N bits, restador paralelo de N bits, etc., que generalmente forman parte de una ALU.

Media sumadora –

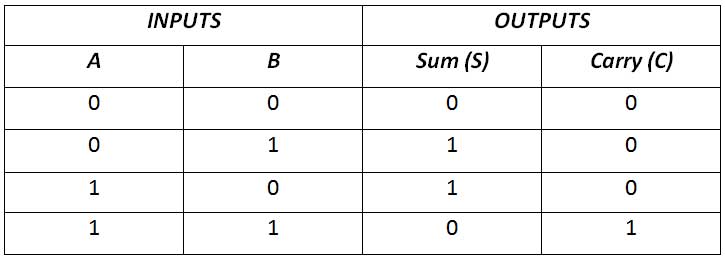

El medio sumador es un circuito combinacional simple que realiza la suma aritmética de dos dígitos binarios o la suma de dos bits. Tiene dos entradas y dos salidas. Las dos entradas son los dos números de 1 bit A y B, mientras que las dos salidas son la suma (S) de A y B y el acarreo (C). La tabla de verdad para un medio sumador es la siguiente:

Figura 1: Tabla de verdad de la mitad del sumador

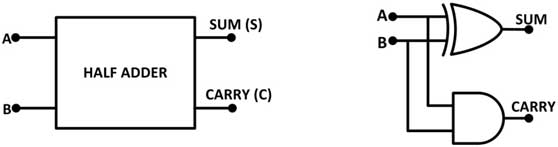

De la tabla de verdad anterior debe quedar claro que la suma es 1 si cualquiera de las dos entradas es 1; de lo contrario, si ambas entradas son 1 o 0, entonces la suma es 0. Esto se puede implementar conectando las entradas a un OR exclusivo. puerta. . El acarreo es 1 solo si ambas entradas son 1; de lo contrario, es 0. Esto se puede implementar conectando las entradas a la puerta AND. Por lo tanto, el medio sumador tiene el siguiente circuito:

Fig. 2: Diagrama de símbolo y puerta lógica del medio sumador

Sumador completo –

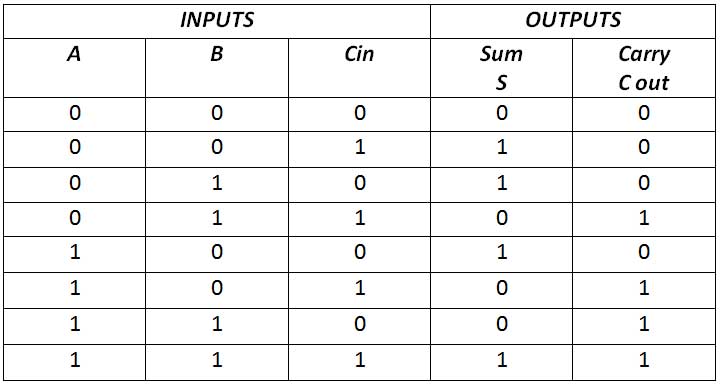

Un medio sumador tiene sólo dos entradas y no hay posibilidad de agregar un acarreo de los bits de orden inferior cuando se realiza una suma múltiple de bits. Para ello se diseña un sumador completo. Un sumador completo está diseñado para realizar una suma aritmética de tres bits de entrada y produce una salida de suma y un acarreo. La tabla de verdad para un sumador completo es la siguiente:

Fig. 3: Tabla de verdad del sumador completo

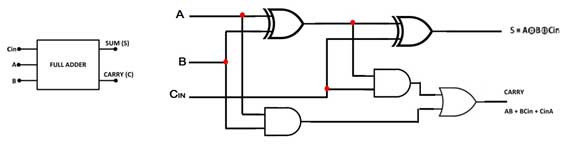

De la tabla de verdad, debería quedar claro que el sumador completo tiene tres entradas y dos salidas. Las dos variables de entrada se indican con A y B, que representan los dos bits significativos que se van a sumar. La tercera entrada Cin representa el acarreo desde la posición anterior de baja importancia. Las salidas son suma (S) y acarreo (C). En la tabla de verdad, se puede ver que la suma es 1 si una de las entradas es 1 o todas las entradas son 1. Esto se puede implementar mediante OR exclusivo de todas las entradas. El acarreo es 1 cuando dos entradas son 1 o todas las entradas son 1. Esto se puede implementar como la suma de la expresión del producto de todas las entradas. Por lo tanto, el sumador completo tiene el siguiente circuito:

Fig. 4: Símbolo y diagrama de puerta lógica del sumador completo

Se puede observar que el sumador completo está formado por dos circuitos semisumadores y una puerta OR.

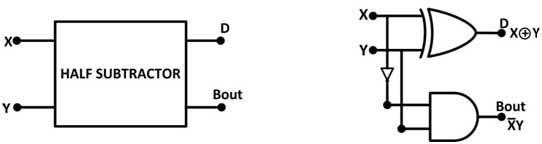

Medio restador –

El medio restador es un circuito combinacional simple diseñado para realizar la resta de dos bits. Tiene dos entradas, X e Y y dos salidas Diferencia (D) y Préstamo (Bout). La tabla de verdad para un medio restador es la siguiente:

Fig. 5: Tabla de verdad del medio restador

En la tabla de verdad se puede ver que la diferencia D es 1 si una de las entradas es 1; de lo contrario, si ambas entradas son 1 o 0, D es 0. Esto se puede implementar conectando las entradas a una puerta OR exclusiva. El préstamo (Bout) es 1 solo si Y es 1 pero no X. El préstamo Bout es 1 siempre que X es menor que Y, por lo que la resta se realiza tomando prestado 1 del siguiente bit de orden superior. Esto se puede implementar mediante la operación Y entre Y y NO de X. Por lo tanto, el medio restador tiene el siguiente circuito:

Fig. 6: Diagrama de símbolo y puerta lógica del medio restador

Restador completo –

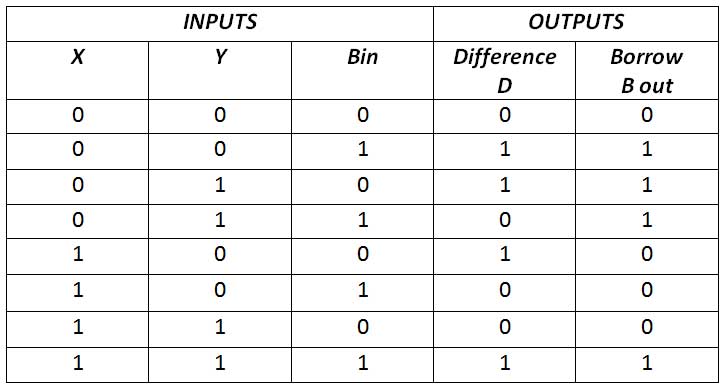

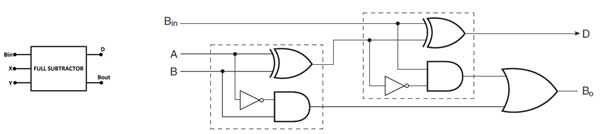

Un restador completo está diseñado para realizar restas que involucran tres bits, es decir, bit de minuendo, bit de resta y préstamo de la etapa anterior. En el restador completo, tiene tres entradas X, Y y Bin, y dos salidas Diferencia (D) y Préstamo (Bout). Existe la siguiente tabla de verdad:

Fig. 7: Tabla de verdad completa del restador

En la tabla de verdad, se puede ver que la diferencia es 1 si una de las entradas es 1 o todas las entradas son 1. Esto se puede implementar mediante OR exclusivo de todas las entradas. El préstamo es 1 si dos entradas son 1 o todas las entradas son 1. Esto se puede implementar como una operación OR entre dos medios restadores. Por lo tanto, el restador completo tiene el siguiente diagrama de circuito:

Fig. 8: Diagrama de símbolo y puerta lógica del restador completo

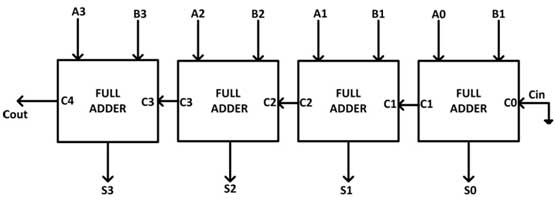

Sumador paralelo de N bits –

Full Adder es capaz de sumar solo dos números binarios de un solo dígito junto con una entrada de acarreo. En la práctica, es necesario sumar números binarios que sean mucho más largos que un solo bit. Para sumar dos números binarios de n bits, debe utilizar el sumador paralelo de n bits. Utiliza múltiples sumadores completos en cascada. La salida de transporte del sumador completo anterior se conecta a la entrada de transporte del siguiente sumador completo.

Como sumador paralelo de 4 bits, se puede construir conectando en cascada cuatro circuitos sumadores completos. En el circuito, A0 y B0 representan el LSB de las palabras de cuatro bits A y B, donde Full Adder-0 es la etapa más baja. Por lo tanto, su Cin se ha hecho permanentemente 0. El resto de las conexiones son exactamente iguales que el sumador paralelo de n bits. El sumador paralelo de cuatro bits es un circuito lógico muy común. Un sumador paralelo de 4 bits se puede mostrar mediante el siguiente diagrama de bloques:

Fig. 9: Diagrama de puerta lógica de sumador paralelo de 4 bits

Restador paralelo de N bits –

La resta se puede realizar tomando el complemento a 1 o 2 del número que se va a restar. Por ejemplo, la resta (AB) se puede realizar sumando el complemento a 1 o 2 de B a A. Por lo tanto, se puede utilizar un sumador binario para realizar la resta binaria. Así como se puede implementar un sumador binario paralelo conectando en cascada múltiples sumadores completos, también se puede implementar un restador binario paralelo conectando en cascada múltiples restadores completos.

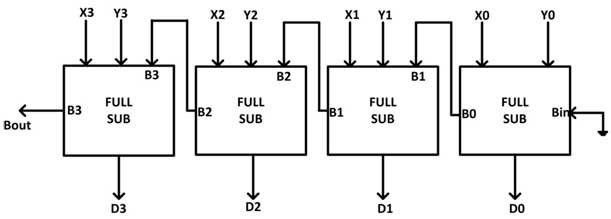

Como restador paralelo binario de 4 bits que resta un número de 4 bits Y3 Y2 Y1 Y0 de otro número de 4 bits X3 X2 X1 X0 tendrá 4 salidas diferentes y una salida prestada (Bout). El Bin del restador completo LSB está conectado a 0 y el Bout del restador completo anterior está conectado al Bin del siguiente restador completo. Un restador paralelo de 4 bits se puede mostrar mediante el siguiente diagrama de bloques:

Fig. 10: Diagrama de puerta lógica de restador paralelo de 4 bits

En el siguiente tutorial, aprenderá sobre la minimización del nivel de puerta y la implementación de puerta lógica de los circuitos aritméticos discutidos anteriormente.