En el tutorial anterior, se discutieron los conceptos básicos de los circuitos lógicos secuenciales . Se mencionó que los circuitos secuenciales pueden ser de dos tipos: síncronos y asíncronos. Los circuitos secuenciales se diferencian de los circuitos combinacionales en la forma en que tienen elementos de memoria para la retroalimentación de estados de entrada anteriores. Los circuitos asíncronos utilizan pestillos como elementos de memoria. Los pestillos no se pueden utilizar como elementos de memoria en circuitos síncronos, ya que los circuitos síncronos requieren dispositivos sensibles a la transición para funcionar contra señales de reloj. Entonces, para circuitos síncronos, los flip-flops se utilizan como elementos de memoria.

Las propias chanclas están construidas sobre pestillos. Para hacer un flip-flop, la operación del pestillo básico se modifica proporcionando una entrada de control adicional que determina cuándo se debe cambiar el estado del circuito. Básicamente, el pestillo con la entrada de control adicional se llama flip-flop. La entrada de control adicional es la entrada de reloj o habilitación.

Los flip-flops se clasifican en diferentes tipos dependiendo de cómo sus entradas y pulsos de reloj causan la transición entre dos estados. Hay cuatro tipos básicos de chanclas:

1 ) Flip-Flop SR-R

2 ) Flip-Flop J-K

3 ) Chanclas D

4 ) T flip-flop

Chanclas SR –

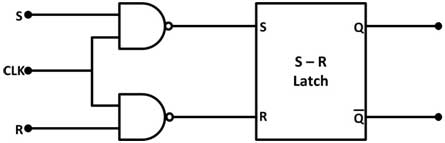

El flip-flop SR es simplemente el pestillo SR con entrada de habilitación. El bloqueo SR con entrada Habilitar se describió en el tutorial anterior. Este es el flip-flop más simple. El pestillo SR está construido por dos puertas NOR acopladas en cruz. La entrada Enable se agrega conectando dos puertas NAND adicionales al circuito de cierre SR básico. Por lo tanto, el flip-flop SR tiene dos salidas Q y Q' que son complementarias entre sí y tres entradas: Set (S), Reset (R) y Enable (En). El pulso de reloj se aplica a la entrada de habilitación. El flip-flop cambia de estado solo cuando se establece en ALTO (si la entrada de habilitación está activa en nivel alto) o cuando se establece en BAJA (si la entrada de habilitación está activa en nivel bajo). La entrada de habilitación se puede activar en nivel bajo conectando un puerto inversor antes. El Flip Flop SR tiene el siguiente diagrama de puerta lógica:

![]()

Fig. 1: Diagrama de puerta lógica del flip-flop SR

Se puede representar mediante el siguiente diagrama de bloques:

Fig. 2: Diagrama de bloques del flip-flop SR

Funciona de acuerdo con la siguiente tabla de funciones:

Figura 3: Tabla de verdad del flip-flop SR

Se puede ver en la tabla de funciones que cuando S = 0 y R = 0 la salida de las puertas NAND 3 y 4 se ve obligada a convertirse en 1. Por lo tanto, R' y S' serán iguales a 1. Dado que S' y R' son la entrada del pestillo SR básico que utiliza puertas NAND, no habrá cambios en el estado de las salidas. Cuando S = 0 y R = 1, dado que S = 0, la salida de NAND-3, es decir, R' = 1 y E = 1, la salida de NAND-4, es decir, S' = 0. Por lo tanto, Qn+ 1 = 0 y Qn+1 barra = 1. Esto se llama enfermedad de reinicio. Cuando S = y R = 0, salida de NAND-3, es decir, R' = 0 y salida de NAND-4, es decir, S' = 1. Por lo tanto, la salida del pestillo SR NAND es Qn+1 = 1 y Qn+1 bar = 0. Esto se llama condición establecida. Dado que S = 1, R = 1 y E = 1, la salida de ambas puertas NAND 3 y 4 es 0, es decir, S' = R' = 0. Por lo tanto, la condición prohibida ocurrirá en el pestillo NAND básico.

D flip-flop –

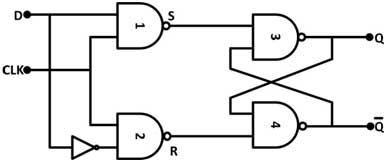

El D Flip Flop está construido a partir del pestillo D. Está diseñado para evitar condiciones prohibidas en el flip-flop SR. El flip-flop D (Delay) tiene solo una entrada llamada entrada de retardo, las dos salidas Q y Ǭ y la entrada Enable para recibir pulsos de reloj. AD Flip Flop se construye acoplando entradas a puertas NAND en un SR Flip Flop. Al acoplar las puertas NAND en el primer nivel de la implementación de la puerta lógica del Flip Flop D, la entrada de datos se conecta directamente a la entrada Set (S) del pestillo SR mientras se conecta a través de un inversor al Reset (R). entrada del pestillo SR. Por lo tanto, cuando Data (D) es 0, Set es 0 y Reset es 1, mientras que cuando D es 1, Set es 1 y Reset es 0. El flip-flop AD tiene el siguiente diagrama de puerta lógica:

Fig. 4: Diagrama de puerta lógica del flip-flop D

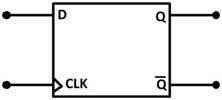

El flip-flop AD se puede representar mediante el siguiente diagrama de puerta lógica:

Fig. 5: Diagrama de bloques del flip-flop D

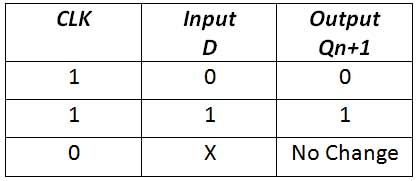

El D Flip Flop funciona según la siguiente tabla de funciones:

Figura 6: tabla de verdad del flip-flop D

En la tabla de funciones, se puede ver que cuando la entrada CLK está en un nivel BAJO, la entrada D no tiene ningún efecto, ya que las entradas de configuración y reinicio del deslizador NAND se mantienen ALTAS. Cuando CLK pasa a nivel ALTO, la salida Q tomará el valor de la entrada D. Si CLK = 1 y D = 1, la salida de la puerta NAND -1 va a 0, que es la entrada de la barra S del flip-over SR básico basado en NAND. flop y NAND gate-2 va a 1, que es la entrada de la barra R del flip-flop SR básico basado en NAND . Por lo tanto S bar = 0 y R bar = 1, la salida será 1, es decir, sigue a la entrada D. Para CLK = 1 y D = 0, la salida será 0. Si D cambia mientras CLK está ALTO, Q seguirá y cambiará rápidamente.

De la tabla de funciones queda claro que el siguiente estado del flip-flop en cualquier momento (Qn +1) sigue el valor de la entrada D cuando se aplica el pulso de reloj. Dado que la transferencia de datos de la entrada a la salida se retrasa, esto se conoce como flip-flop de retardo (D). El flip-flop D se utiliza como dispositivo de retardo o como pestillo para almacenar 1 bit de información binaria.

Zapatilla JK del maestro esclavo –

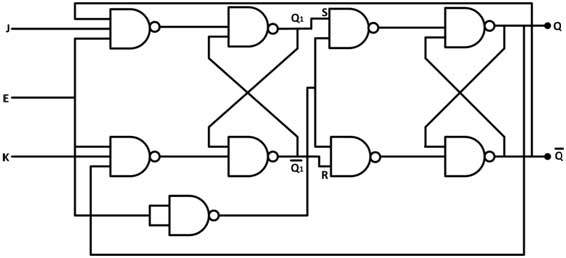

El flip-flop Master Slave JK fue diseñado para evitar condiciones prohibidas en el flip-flop SR, además de eliminar el problema de sincronización para responder a niveles altos y bajos del pulso de reloj. El Flip-Flop Master Slave JK se construye conectando dos flip-flops SR en cascada con retroalimentación desde la salida del segundo a la entrada del primero. De esta manera, el flip-flop Master se activa con un nivel positivo. Pero debido a la presencia del inversor en la línea del reloj, el esclavo responderá al nivel negativo. Por lo tanto, cuando la señal de reloj es 1 (nivel positivo), el maestro está activo y el esclavo está inactivo. Cuando el reloj está en 0 (nivel bajo), el esclavo está activo y el maestro está inactivo.

El flip-flop JK tiene tres entradas J, K y entrada Enable, mientras que dos salidas Q y Q'. El JK Flip Flop tiene el siguiente diagrama de puerta lógica:

Fig. 7: Diagrama de puerta lógica del flip-flop Master Slave JK

Funciona de acuerdo con la siguiente tabla de funciones:

Fig. 8: Tabla de verdad de Flip Flop Master Slave JK

En la función de la tabla se puede ver que hay cuatro salidas posibles de los flip-flops JK como se menciona a continuación:

Caso 1 – J. = K = 0 (Sin cambios): Cuando la señal del reloj es 0, el esclavo está activo y el maestro está inactivo. Pero como las entradas S y R no han cambiado, las salidas esclavas tampoco cambiarán. Por lo tanto, las salidas no cambiarán si J y K son 0.

Caso 2 – J. = 0 y K = 1 (Reset): Cuando la señal del Reloj es 1, el Maestro está activo mientras el esclavo está inactivo. Por lo tanto, las salidas maestras se vuelven Q1 = 0 y Q1 bar = 1. Esto significa que S se vuelve 0 y R se vuelve 1. Cuando la señal del Reloj es 0, el Esclavo está activo mientras el maestro está inactivo. Por lo tanto, las salidas esclavas pasan a ser Q = 0 y Q bar = 1. Nuevamente, cuando la señal del reloj es 1, el Maestro está activo y el esclavo está inactivo. Por lo tanto, incluso con las salidas modificadas (Q = 0 y Q bar = 1) devueltas al maestro, su salida será Q1 = 0 y Q1 bar = 1. Esto significa que S se convierte en 0 y R se convierte en 1. Por lo tanto, con Si la señal de reloj es 0 y el esclavo se activa, las salidas del esclavo permanecerán Q = 0 y Q bar = 1. Por lo tanto, hay una salida estable del Maestro y el Esclavo.

Caso 3 – J. = 1 y K = 0 (Set): Cuando la señal del Reloj es 1, el Maestro está activo y el esclavo está inactivo. Por lo tanto, las salidas maestras se vuelven Q1 = 1 y Q1 bar = 0. Esto significa que S se establece en 1 y R se establece en 0. Cuando la señal del Reloj es 0, el Esclavo está activo y el Maestro está inactivo. Por lo tanto, las salidas esclavas pasan a ser Q = 1 y Q bar = 0. Nuevamente, cuando la señal de reloj es 1, se puede ver que las salidas esclavas se estabilizan en Q = 1 y Q bar = 0.

Caso 4 – J. = K = 1 (Alternar): Cuando la señal del Reloj es 1, el Maestro está activo y el esclavo está inactivo. Se conmutarán las salidas maestras. Entonces S y R también se invertirán. Cuando la señal del Reloj es 0, el Esclavo está activo y el Maestro está inactivo. Se conmutarán las salidas esclavas. Estas salidas modificadas se devuelven a las entradas maestras. Pero cuando la señal del reloj es 0, el maestro sigue inactivo. Por lo tanto, no responde a estos resultados modificados. Esto evita múltiples cambios que conducen a una condición de carrera. El flip-flop maestro-esclavo es útil para evitar la condición de carrera del flip-flop SR.

zapatilla T –

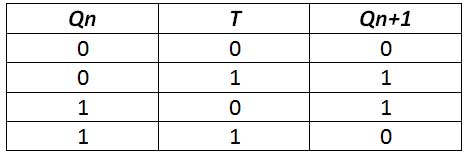

El flip-flop T o Toggle Flip Flop cambia su salida en cada transición de reloj. Es otro flip-flop básico que tiene una sola entrada de datos (T), una entrada de reloj y dos salidas Q y Ǭ. El flip-flop tipo T se construye a partir del flip-flop JK conectando sus entradas J y K. La T representa la capacidad del flip-flop para alternar o complementar su estado. AT Flip Flop está representado por el siguiente diagrama de bloques:

Fig. 9: Diagrama de bloques del flip-flop T

El T Flip Flop se puede construir conectando las entradas J y K del flip flop JK juntas. De esta manera, el flip-flop JK solo puede ingresar al estado sin cambios o al estado de conmutación. El T Flip Flop está construido a partir del JK Flip Flop de la siguiente manera:

Fig. 10: Diagrama de puerta lógica del flip-flop T

El T Flip Flop funciona según la siguiente tabla de funciones:

Fig. 11: Tabla de verdad del flip-flop T

En la tabla de funciones, se puede ver que cuando la entrada T está en estado 0 (es decir, J = K = 0) antes del pulso de reloj, la salida Q no cambiará con el tiempo . Cuando la entrada T se establece en 1 nivel (es decir, J = K = 1) antes de la sincronización , la salida estará en el estado Ǭ después de la sincronización. En otras palabras, si la entrada T es 1 lógico y el dispositivo está sincronizado, la salida cambiará de estado independientemente de qué salida estaba antes de la entrada. momento . Entonces, cuando T = 0, entonces Qn+1 = Qn, es decir, el siguiente estado es igual al estado actual y no se produce ningún cambio. Cuando T = 1, entonces Qn+1 = Ǭn, es decir, el estado del flip-flop se complementa. Esto se llama alternancia, por lo que el flip-flop recibió el nombre de flip-flop T.

Los flip-flops son una parte esencial de cualquier circuito síncrono. Pueden almacenar un bit a la vez. Se utilizan grupos de flip-flops para almacenar datos en circuitos síncronos prácticos. En el siguiente tutorial, aprenderá sobre los registros .