Por Krupa BhavsarEngenheiro de Aplicações, Dialog Semiconductor

As ondas senoidais são ondas contínuas, que descrevem uma oscilação periódica suave. Essas ondas são geralmente usadas em processamento de sinais e campos de engenharia

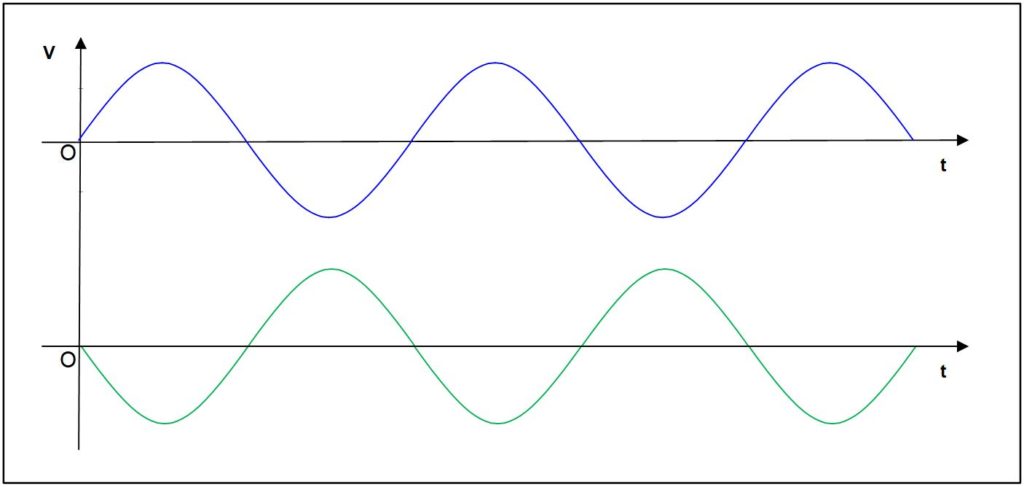

Neste artigo, ondas senoidais duplas com polaridade oposta, conforme mostrado em figura 1 são gerados sem “etapas” grosseiras de PWM. Para gerar ondas senoidais, é utilizada uma macrocélula PWM. A macrocélula PWM possui tabela pré-programada com valores de Duty Cycle PWM para cada “passo” da onda senoidal.

Figura 1. Ondas senoidais com polaridade oposta

Este projeto está dividido em três seções. A seção Geração de frequência de relógio descreve cálculos para gerar uma nova frequência de onda senoidal desejada. Na seção HV PAK, o projeto do circuito é mostrado e explicado. Finalmente, a seção Configuração de Teste e Expansão Futura fornece detalhes adicionais sobre as condições de teste e outras possibilidades que este projeto tem.

Geração de frequência

A geração da onda senoidal é dividida em 2 partes. Os valores pré-programados do Ciclo de Trabalho de uma parte da onda armazenados no arquivo Reg da macrocélula PWM e aumentam após a chegada de cada clock. Quando o número de clocks é igual ao número de bits do arquivo Reg, a entrada Up/Down do estado da macrocélula PWM muda e o arquivo Reg começa a sincronizar na direção oposta.

A nova geração de frequência de clock depende da frequência da onda senoidal. O número de períodos PWM necessários para uma frequência da onda senoidal.Equação 1

Onde, – frequência de onda senoidal desejada, – número de bits pré-programados, por padrão é 16.

Projeto HVPAK

Neste projeto, usamos o circuito GreenPAK

Neste projeto, usamos o circuito GreenPAK para ilustrar como o gerador de onda senoidal pode ser construído – especificamente SLG47105 High Voltage GreenPAK (HVPAK). O arquivo completo do projeto do circuito criado no software GreenPAK Designer (disponível gratuitamente) pode ser encontrado aqui.

para ilustrar como o gerador de onda senoidal pode ser construído – especificamente SLG47105 High Voltage GreenPAK (HVPAK). O arquivo completo do projeto do circuito criado no software GreenPAK Designer (disponível gratuitamente) pode ser encontrado aqui.

A Figura 2 mostra o projeto. Este design requer apenas uma entrada externa, ou seja, entrada EN. Neste projeto, a macrocélula PWM0 é configurada como um gerador controlado por frequência que gera sinal PWM para cada parte de uma onda senoidal. As saídas da macrocélula PWM0 são conectadas ao HV OUT CTRL0 que é então conectado aos filtros externos para obter ondas senoidais duplas com polaridade reversa.

Neste projeto, o projeto HVPAK está configurado para gerar uma onda senoidal de 1kHz.

O CNT0/DLY0/FSM0 está configurado como Reset Counter. O período de saída CNT0/DLY0/FSM0 determina um período de cada etapa do arquivo Reg e a frequência da onda senoidal de saída (1).

De acordo com (1) para gerar uma frequência de onda senoidal de saída de cerca de 1kHz, a frequência de saída CNT0/DLY0/FSM0 deve ser igual a 31,25kHz ou período de saída 32us.

A direção do PWM muda a cada período de clock de 16s. CNT1/DLY1 conta 16 períodos de clock do sinal de entrada. O DFF6 é configurado como um flip-flop alternado que muda a direção da macrocélula PWM.

A macrocélula HV OUT CTRL0 está configurada em configuração de controle no modo Half-Bridge. O PWM0 OUT+ está conectado a IN0 e a saída OUT- está conectada a IN1. As entradas OE0 e OE1 estão conectadas ao POR. As entradas de suspensão são usadas para desabilitar HV OUT CTRL0 quando o sinal EN está no estado Baixo.

Um par de filtros RC externos é necessário para suavizar os sinais PWM e receber ondas senoidais sem ruído.

O flip-flop DFF3 e o LUT1 de 2 bits são usados para pular a primeira metade do período após a partida do gerador. A onda senoidal do primeiro canal começa em 100% do ciclo de trabalho enquanto o filtro RC de saída está descarregado. Neste caso, metade do primeiro período da onda senoidal do canal 1 fica totalmente distorcida.

Assim, para gerar uma onda senoidal de uma frequência desejada usando uma frequência de entrada desejada, o projetista primeiro calcula os parâmetros necessários para modificar as macrocélulas conforme descrito na seção Geração de frequência de relógio e, em seguida, modifica as configurações da macrocélula PWM e CNT de acordo com descrito acima.

Teste configuração e expansão futura

Teste configuração e expansão futura

Este projeto é testado usando filtros RC externos e um botão. O botão de pressão é conectado à entrada EN e cada filtro RC é conectado às saídas HV da macrocélula HV OUT CTRL0, conforme mostrado na Figura 3. Conforme mostrado na Figura 4, aproximações de onda senoidal dupla com polaridade oposta são geradas quando a entrada EN é HIGH.

Figura 3. Configuração de teste

Canal 1 (linha amarela/superior) – Pino nº 2 (EN)

Canal 2 (ciano/2ª linha) – Saída de onda senoidal no pino nº 7 (TP1)

Canal 3 (magenta/3ª linha) – Saída de onda senoidal no pino nº 8 (TP2)

Figura 4. Saídas de onda senoidal

As possibilidades futuras deste projeto podem ser expandidas para gerar ondas senoidais através de um MCU habilitado para I2C em vez de um botão, alterar a frequência da onda senoidal e também incluir recursos de proteção como limite de corrente/corrente constante usando Comparador de detecção de corrente e bloqueio de subtensão ( UVLO). Este projeto também pode ser expandido para gerar ondas senoidais duplas adicionais usando a macrocélula HV OUT CTRL 1.

Conclusão

O projeto HVPAK descrito neste artigo gera duas aproximações de onda senoidal de 1kHz. O design é fácil de usar, minimiza custos, economiza espaço na placa e contagem de componentes.

Além disso, o circuito que usamos é bastante flexível, fácil de testar e pode acomodar alterações de última hora no projeto. Uma vez modificado o projeto, um novo arquivo de projeto pode ser programado no chip e soldado novamente na placa. Ele também oferece segurança de projeto, bloqueando o arquivo de projeto para limitar a visibilidade. Ao usar este design, o usuário pode gerar ondas senoidais com a frequência desejada usando macrocélulas PWM e uma única entrada.