Nota: é recomendado seguir esta série de tutoriais VHDL em ordem, começando com o primeiro tutorial.

No tutorial anterior – Tutorial VHDL 16 – projetamos um circuito flip-flop D usando VHDL.

Para este projeto, iremos:

- Escreva um programa VHDL para construir um circuito flip-flop JK

- Verifique a forma de onda de saída do programa (o circuito digital) com a tabela verdade do flip-flop.

O flip-flop JK com um circuito predefinido e claro:

Tabela verdade

- Nota 1: quando J=1 e K=1, a saída Q alterna sempre (de 0 a 1 e 1 a 0)

- Nota 2: quando J=0 e K=0, a saída Q mantém seu estado anterior

Agora vamos escrever, compilar e simular um programa VHDL. Então, obteremos a saída em forma de onda e a verificaremos com a tabela verdade fornecida.

Antes de começar, certifique-se de revisar o procedimento passo a passo fornecido em Tutorial VHDL – 3 projetar adequadamente o projeto, bem como editar e compilar o programa e o arquivo de forma de onda, incluindo a saída final.

Aqui. usamos um estilo de modelagem comportamental para escrever o programa VHDL e construir o circuito flip-flop porque é o modelo preferido para circuitos digitais sequenciais.

Programa VHDL

biblioteca ieee;

use ieee.std_logic_1164.all;

entidade JK_flip_flop é

porta (clk,J,K,prs,clr: em std_logic;

P: fora std_logic;

Qnot: fora std_logic);

fim JK_flip_flop;

arquitetura JKFF_arch de JK_flip_flop é

sinal nxt_state, prv_state: std_logic;

entrada de sinal: std_logic_vector(1 até 0);

começar

entrada <= J e K;

processo(clk, prs,clr) é

começar

se (clr='1′) então

nxt_state <= '0';

elsif (prs='1′) então

nxt_state <= '1';

elsif (clk'event e clk='1′) então

caso (entrada) é

quando “10” => nxt_state <= '1';

quando “01” => nxt_state <= '0';

quando “00” => nxt_state <= prv_state;

quando “11” => nxt_state <= não prv_state;

quando outros => nulo;

fim do caso;

fim se;

fim do processo;

Q <= estado_nxt;

Qnot <= não nxt_state;

prv_state <= nxt_state;

fim JKFF_arch;

Para refrescar sua memória sobre como isso funciona, leia os dois primeiros tutoriais do VHDL (1 e 2) desta série.

Em seguida, compile o programa acima, criando e salvando um arquivo de forma de onda com todas as entradas e saídas necessárias listadas (e certifique-se de aplicar todas as diferentes combinações de entrada). Em seguida, simule o projeto. Você deve obter o seguinte resultado…

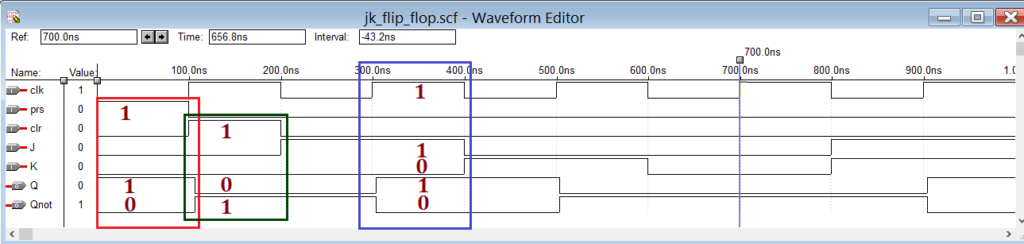

Forma de onda de simulação Conforme mostrado nesta figura, há três casos destacados em vermelho, verde e azul:

Conforme mostrado nesta figura, há três casos destacados em vermelho, verde e azul:

- Caso 1: quando prs=1 -> Q = 1 e Qnot = 0 (o flip-flop está setado)

- Caso 2: quando clr=1 -> Q=0 e Qnot = 1 (o flip-flop está limpo)

- Caso 3: quando J=1, K=0 e clk=1 – > Q = 1 e Qnot = 0

Certifique-se de verificar as diferentes combinações de entrada-saída com a tabela verdade fornecida.

No próximo tutorial, aprenderemos como construir um circuito flip-flop T usando VHDL.