O AVR (ATmega32) contém alguns registros integrados para comunicação TWI que não apenas reduzem o nível de complexidade, mas também facilitam todo o processo de comunicação.

Esses registros foram explicados neste tutorial.

1. TWBR (registro de taxa de bits TWI):

|

TWBR7

|

TWBR6

|

TWBR5

|

TWBR4

|

TWBR3

|

TWBR2

|

TWBR1

|

TWBR0

|

Este registro é usado no modo mestre para definir o fator de divisão do gerador de taxa de bits (frequência de clock SCL). A unidade geradora de taxa de bits controla o período de tempo do SCL. A frequência do clock SCL é decidida pelo Bit Rate Register (TWBR) e pelos bits prescaler do registro TWSR (explicados a seguir).

2. TWSR (registro de status TWI):

|

TWS7

|

TWS7

|

TWS7

|

TWS7

|

TWS7

|

–

|

TWPS1

|

TWPS0

|

· Bits7-3 – TWS: Status do TWI

Esses bits refletem o status de TWI barramento que será explicado posteriormente na explicação do código. O artigo concentra-se apenas nas condições de status que serão utilizadas nos códigos. Para obter mais detalhes sobre o restante do status, consulte a folha de dados.

· Bit 2- Bit reservado

· Bits1-0 – TWPS: Bits pré-escaladores TWI

Esses bits são usados para definir o pré-escalador da 'Unidade geradora de taxa de bits'.

|

TWPS1

|

TWPS0

|

Valor do pré-escalador

|

|

0

|

0

|

1

|

|

0

|

1

|

4

|

|

1

|

0

|

16

|

|

1

|

1

|

64

|

Valor do Prescaler de acordo com bits TWPS

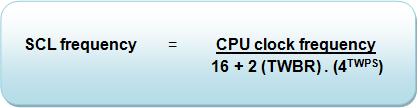

Fórmula para frequência de clock SCL:

Fig. 1: Imagem mostrando a fórmula para frequência de clock SCL

3. TWDR (registro de dados TWI):

|

TWD7

|

TWD6

|

TWD5

|

TWD4

|

TWD3

|

TWD2

|

TWD1

|

TWD0

|

O TWDR sempre contém os últimos dados presentes no barramento SDA. No modo transmissor, o TWDR contém o próximo byte a ser transmitido. Enquanto estiver no modo de recepção, o TWDR contém o último byte recebido. Os dados no TWDR permanecem estáveis enquanto o sinalizador TWINT estiver alto.

Contínuo

4. TWCR (registro de controle TWI):

|

TWINT

|

TWEA

|

TWSTA

|

TWSTO

|

TWWC

|

DOZE

|

–

|

DOIS

|

· Bit 7 – TWINT: Flag de interrupção TWI

Este bit é usado para monitorar o status atual do TWI. O TWINT é definido pelo hardware quando o TWI termina seu trabalho atual. O SCL ficará baixo até que o bit TWINT seja definido. O sinalizador TWINT deve ser apagado pelo software antes de iniciar qualquer operação no TWI.

Nota: O sinalizador TWINT é limpo escrevendo um lógico nele.

· Bit 6 – TWEA: Bit de reconhecimento de habilitação de TWI

O bit TWEA é usado para gerar o pulso de confirmação. Se o bit TWEA for escrito em um, o pulso ACK será gerado. E por outro lado, se o bit TWEA for zero, o dispositivo pode ser virtualmente desconectado temporariamente do barramento serial de dois fios.

Nota: Os valores de status do TWI são diferentes quando os dados são transferidos com base no recebimento do pulso ACK (TWEA está definido) ou NOT ACK (TWEA está limpo).

· Bit 5 – TWSTA: Bit de Condição TWI START

Ao escrever um neste bit, o dispositivo se torna um controlador mestre. Ele verifica se o barramento está disponível (o barramento não está ocupado na transmissão para outros mestres) e então gera a condição de partida no barramento. Se o barramento não estiver livre, o TWI espera até que uma condição STOP seja detectada e então gera uma nova condição START para reivindicar ser o mestre do barramento.

· Bit 4 – TWSTO: Bit de Condição TWI STOP

Ao escrever um no bit TWSTO, o mestre irá gerar uma condição STOP no barramento serial de dois fios. Quando a condição STOP é executada no barramento, o bit TWSTO é zerado automaticamente.

· Bit 3 – TWWC: Sinalizador de colisão de gravação TWI

Este bit é usado para evitar a colisão na escrita no TWDR. O bit TWWC será definido quando o TWDR estiver tentando escrever (o sinalizador TWINT está baixo). O sinalizador TWWC é apagado escrevendo TWDR quando TWINT está alto.

· Bit 2 – TWEN: Bit de habilitação de TWI

O bit TWEN é usado para ativar/desativar a interface TWI. Quando este bit é escrito em um, a operação TWI é habilitada. Se este bit for escrito em zero, o TWI será desligado e a transmissão do TWI será encerrada.

· Bit 1 – Bit reservado e sempre escrito como zero.

· Bit 0 – TWIE: Habilitação de interrupção TWI

O bit TWIE é usado para ativar/desativar a solicitação de interrupção TWI. A solicitação de interrupção é habilitada gravando um nela e desabilitada gravando zero nela.

5. TWAR (registro de endereço TWI (escravo)):

|

TWA6

|

TWA5

|

TWA4

|

TWA3

|

TWA2

|

TWA1

|

TWA0

|

TWGCE

|

· Bits 7-1 – TWA: Bits de endereço TWI (escravo)

Esses bits são usados para armazenar endereços escravos de 7 bits aos quais o TWI responde quando programado como Transmissor ou Receptor Escravo.

· Bit 0 – TWGCA: Bit de habilitação de reconhecimento de chamada geral TWI

Este bit é usado para permitir que o escravo reconheça o endereço de chamada geral (0x00).

A chamada geral aborda todos os dispositivos no barramento usando o I2Endereço C 0.

Se um dispositivo não precisar das informações fornecidas, ele simplesmente não fará nada. Os dispositivos que processam a mensagem reconhecem este endereço e se comportam como receptores escravos.

O mestre não consegue detectar quantos dispositivos estão usando a mensagem. O segundo byte contém um comando.

Veja também a interface do TWI com o ATmega32