Como a miniaturização eletrônica tem sido uma meta constante dos fabricantes de chips, os sistemas eletrônicos/computadores baseados em placas-mãe foram eventualmente substituídos por ICs System-on-Chip (SoC) e Package-on-Package (PoP). Sistemas informáticos complexos estão agora condensados em smartphones e outros dispositivos portáteis. Esses sofisticados dispositivos e gadgets eletrônicos têm um SoC em seu coração que gerencia computação e controle completos. O pacote SoC é composto por vários núcleos de propriedade intelectual (IP). Esses núcleos IP vêm de diferentes empresas e fornecedores de design de chips.

Uma comunicação de dados escalável, compatível e eficiente entre vários núcleos IP em um SoC tem sido um desafio. Inicialmente, isso foi feito pelos projetistas de chips por meio de um redesenho trabalhoso, testes de compatibilidade e projeto de interfaces adicionais. Esta abordagem carecia de coerência à primeira vista, o que conduzia a dispendiosos redesenhos futuros. Uma das soluções amplamente aceitas e viáveis para este problema foi introduzida por Arm em 1996 como protocolos AMBA.

O que é AMBA?

AMBA (Advanced Microcontroller Bus Architecture) é um padrão aberto e disponível gratuitamente para interconexão e gerenciamento de núcleos IP em um IC System-on-Chip (SoC). Ele permite o desenvolvimento imediato de designs de chips multiprocessadores de maneira modular, reutilizável e escalável. Isso ajuda a evitar reprojetos dispendiosos e reduz o tempo de lançamento de projetos integrados no mercado.

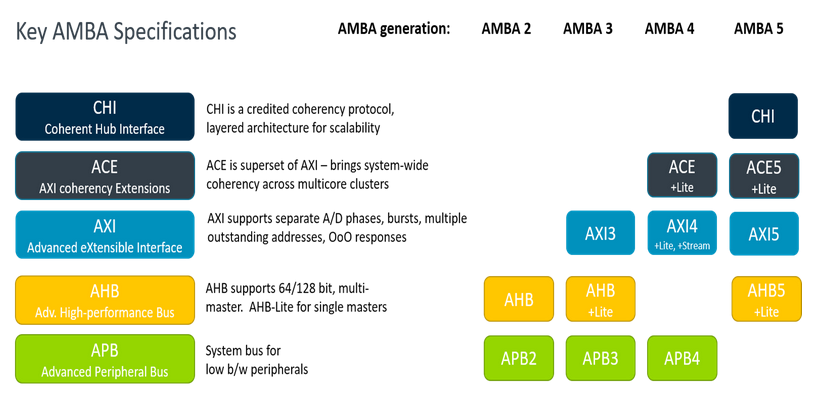

AMBA foi introduzido pela primeira vez em 1996 com especificações Advanced Peripheral Bus (APB) e Advanced System Bus (ASB). A segunda versão do AMBA foi introduzida em 1999 e incluía especificações Advanced High-Performance Bus (AHB). AMBA 3 que incluía Advanced Extensible Interface (AXI), foi introduzido em 2003. AMBA 4 introduziu AXI Coherency Extensions (ACE) em 2010 e AMBA 5, a versão mais recente do AMBA, introduziu Coherent Hub Interface (CHI) em 2013.

Sistema de ônibus AMBA

Sistema de ônibus AMBA

Um design tradicional de SoC baseado em AMBA usa especificações Advanced System Bus (ASB) ou Advanced High-performance Bus (AHB) para comunicação de alta largura de banda com blocos como processador, RAM no chip, interfaces de memória e barramento DMA mestre. Embora use Advanced Peripheral Bus (APB) para comunicação de baixa largura de banda com blocos como UART, GPIO, teclado, display, temporizador, etc., SoCs que possuem um grande número de blocos funcionais ou núcleos IP requerem interconexão ponto a ponto que usa Especificações de interface extensível avançada (AXI). O barramento AXI gerencia a comunicação usando um protocolo mestre-escravo e pode ser facilmente conectado ao APB. Pode haver vários mestres e escravos AXI compartilhando um barramento.

Telefones celulares e smartphones que contêm SoC com vários núcleos de processador compartilhando uma memória cache comum exigem gerenciamento de coerência em todo o subsistema de memória. Para isso, as especificações ACE foram introduzidas no AMBA 4. As especificações AXI/ACE foram redesenhadas como CHI para gerenciar mecanismos de comunicação em sistemas computacionais heterogêneos. Em contraste, para protocolo baseado em sinal nas especificações AXI/ACE, CHI é um protocolo em camadas baseado em pacotes que pode ser ampliado para mecanismos de comunicação entre blocos funcionais heterogêneos, como Processadores de Sinais Digitais (DSP), Unidades de Processamento Gráfico (GPU), E/S subsistemas e controladores de memória.

Especificações AMBA

AMBA é um conjunto de protocolos de interconexão. A versão mais recente AMBA 5 inclui as seguintes especificações:

- APB: A versão mais recente do Advanced Peripheral Bus (APB) foi introduzida no AMBA 2.0. Este é um protocolo simples sem pipeline usado para comunicação mestre-escravo com periféricos de baixa largura de banda. Vários periféricos podem ser conectados a um barramento compartilhado, que é gerenciado através de uma ponte (como a ponte AXI-APB) ou diretamente por um mestre (processador/controlador). Nas especificações APB, o mesmo conjunto de sinais é usado para ler e escrever no barramento e nenhuma transferência de dados em rajada é suportada.

- ASB: O Advanced System Bus (ASB) é um protocolo em pipeline para mecanismos de comunicação com componentes de alta largura de banda e alta frequência. Ele suporta transferências burst e vários barramentos mestres. Este sistema de barramento suporta interconexão entre múltiplos mestres e memórias. O barramento consiste em quatro tipos de blocos – Mestre, Árbitro, Escravo e Decodificador. A qualquer momento, apenas um mestre pode acessar o barramento. Um mestre só pode acessar o barramento com a ajuda de um árbitro enquanto precisa selecionar um escravo para comunicação usando um decodificador. O mestre inicia a operação de leitura ou escrita e o escravo selecionado responde às solicitações de leitura e escrita.

-

AHB: O barramento avançado de alto desempenho (AHB) foi introduzido no AMBA 2.0. É uma alternativa ao ASB onde são necessários recursos de alto desempenho. Ele suporta configurações de barramento de dados mais amplas, transferência mestre de barramento de ciclo único, transações divididas e operações de clock único. Assim como o ASB, o barramento AHB também requer componentes adicionais para gerenciar mecanismos de comunicação, como multiplexador de leitura, multiplexador de gravação, decodificador, árbitro, endereço e multiplexador de controle. O sistema de barramento consiste em três sinais – sinal de endereço, barramento de gravação de dados e barramento de leitura de dados. O sinal de endereço é usado para selecionar um escravo, o barramento de dados de gravação é usado para mover comandos do mestre para o escravo e o barramento de dados de leitura é usado para mover as respostas dos escravos para os mestres. O mestre acessa o barramento solicitando ao árbitro e usa o decodificador para selecionar um escravo. O barramento é atribuído a um mestre com base em um esquema de priorização. Este esquema é definido nas especificações AMBA e difere entre os diferentes designs. Existem 20 sinais AHB diferentes no total, em comparação com 15 sinais em ASB.

- AHB-lite: É uma versão simplificada do AHB. Suporta mecanismos de comunicação com um único mestre sem a necessidade de qualquer árbitro. Também exclui alguns recursos de alto desempenho do AHB, como transações divididas e novas tentativas.

- EIXO: A Advanced Extensible Interface (AXI) é uma especificação de interconexão ponto a ponto que supera as limitações dos protocolos de barramento compartilhado na conexão de vários agentes. Ele foi projetado especificamente para gerenciar mecanismos de comunicação com processadores e controladores multi-core. As especificações AXI foram introduzidas no AMBA 3.0. Em vez de usar um barramento de sistema, ele usa interfaces bem definidas para mecanismos de comunicação de alta largura de banda e baixa latência. Ele possui vários recursos aprimorados em comparação com o AHB, como múltiplas transferências em pipeline, fios separados de leitura/gravação, larguras de barramento de dados mais amplas e transferências de dados em rajada.

- AXI-lite: É uma versão simplificada do protocolo AXI. Falta transferência de dados intermitente em comparação com as especificações AXI completas.

- Fluxo AXI: Esta é uma modificação do protocolo AXI para suportar streaming de dados de mestres para escravos. Neste protocolo, os dados são movidos apenas em uma direção, do mestre para o escravo. Os canais de leitura/gravação não são separados no fluxo AXI, ao contrário da especificação AXI completa. É possível transferir múltiplos fluxos de dados entre mestre e escravo. Este protocolo é útil em aplicações como streaming de vídeo, streaming de jogos, etc.

- ÁS: As especificações AXI Coherency Extensions (ACE) foram introduzidas no AMBA 4.0. Esta especificação é usada para gerenciar mecanismos de comunicação em processadores/controladores multi-core com memórias cache coerentes compartilhadas entre eles. A especificação ACE estende os canais de leitura e gravação AXI usando endereços de snoop separados, canais de dados de snoop e canais de resposta de snoop. Esses canais adicionais implementam protocolo de coerência baseado em espionagem.

- ACE-lite: ACE-lite é uma versão simplificada da especificação ACE completa. Ele foi projetado para gerenciar mecanismos de comunicação com agentes que não possuem memória cache própria, mas ainda podem participar de um sistema de coerência compartilhável usando coerência unidirecional. Exemplos de tais agentes são controladores DMA e blocos Network-on-Chip.

- CHI: A Coherent Hub Interface (CHI) é uma reformulação do protocolo ACE para sistemas de computação heterogêneos e complexos. O protocolo ACE usa interconexão de comunicação mestre-escravo em nível de sinal usando um grande número de fios e canais adicionais para bisbilhoteiros e respostas. Isso funciona bem para pequenos clusters coerentes, como SoCs móveis dual ou quad-core. No entanto, com muitos componentes heterogêneos como DSP, GPU, NPU, etc., o AXI atinge limitações por ainda ser um protocolo baseado em sinal. CHI é uma reformulação do barramento AXI que usa protocolos de interface baseados em pacotes em vez de um sistema de barramento baseado em sinais.

Conclusão

Se você trabalha com design VLSI, provavelmente já ouviu falar ou aprendeu sobre os protocolos AMBA. A AMBA evoluiu ao longo dos anos para atender às necessidades de projetos de SoC de última geração e desenvolvimentos futuros de IC. Os protocolos AMBA são de padrão aberto e podem ser baixados do site da Arm após registro gratuito. Este artigo fornece uma visão geral de várias especificações AMBA. Você pode baixar as especificações do site da Arm e aprender mais sobre esses protocolos de design de chips.