Nota: é recomendável seguir esta série de tutoriais VHDL em ordem, começando com o primeiro tutorial.

No tutorial anteriorprojetamos circuitos de trava SR com clock usando VHDL (que é uma linguagem de descrição de hardware de circuito integrado de altíssima velocidade).

Para este projeto, iremos:

- Escreva um programa VHDL para construir um circuito flip-flop D

- Verifique a forma de onda de saída do programa (circuito digital) com a tabela verdade deste circuito flip-flop

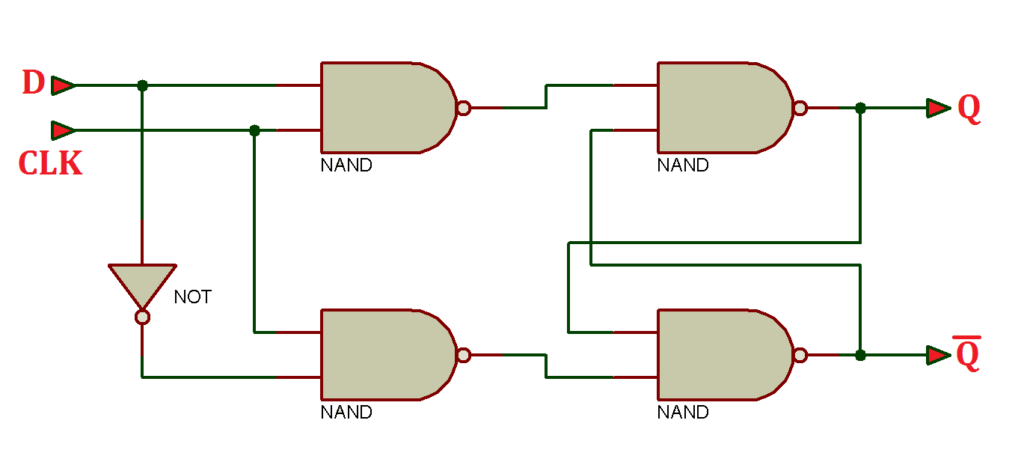

O circuito flip-flop D

Tabela verdade

Agora vamos escrever, compilar e simular um programa VHDL. Então, obteremos a saída em forma de onda e a verificaremos com a tabela verdade fornecida.

Antes de começar, certifique-se de revisar o procedimento passo a passo fornecido em Tutorial VHDL – 3 projetar adequadamente o projeto, bem como editar e compilar o programa e o arquivo de forma de onda, incluindo a saída final.

Para este tutorial, usamos um estilo de modelagem comportamental para escrever o programa VHDL que construirá o circuito flip-flop. Este é o estilo de modelagem preferido para circuitos digitais sequenciais.

Programa VHDL

biblioteca ieee;

use ieee.std_logic_1164.all;

entidade D_flip_flop é

porta (clk,Din: em std_logic;

P: fora std_logic;

Qnot: fora std_logic);

fim D_flip_flop;

arquitetura DFF_arch de D_flip_flop é

começar

processo (clk,Din)

começar

if(clk'evento e clk='1′) então

Q <= Ruído;

Qnot <= (não Din);

fim se;

fim do processo;

fim DFF_arch;

Para refrescar sua memória sobre como isso funciona, leia os dois primeiros tutoriais de VHDL (1 e 2) desta série.

A seguir, compile o programa acima, criando um arquivo de forma de onda com todas as entradas e saídas necessárias listadas, e simule o projeto. Você deve obter o seguinte resultado…

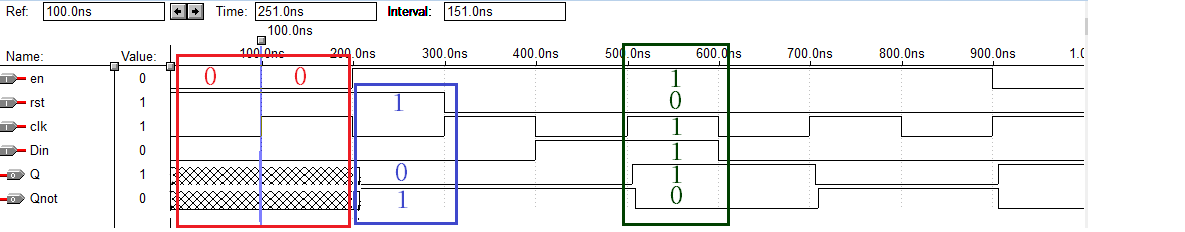

Forma de onda de simulação

Conforme mostrado nesta figura, há dois casos destacados em vermelho e azul.

- Caso 1: quando clk=1 e Din=1 -> Q = 1 e Qnot = 0

- Caso 2: quando clk=1 e Din = 0 -> Q=0 e Qnot = 1

Este programa para o circuito flip-flop D parece bastante simples. Então, vamos complicar um pouco mais adicionando mais dois sinais de entrada:

1. Redefinir: a entrada de reinicialização alta ativa, portanto, quando a entrada for '1', o flip-flop será redefinido e Q = 0, Qnot = 1

2. Habilitar: ativa a entrada para o circuito flip-flop, portanto, se estiver definido como '0', o flip-flop será desabilitado e ambas as saídas estarão em alta impedância (onde '1' é quando o flip-flop opera normalmente)

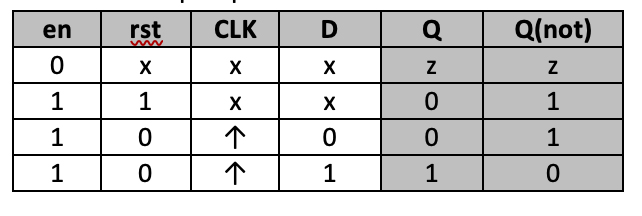

Tabela verdade para o flip-flop D

Agora, aqui está o programa do flip-flop D com as entradas enable e active high reset.

biblioteca ieee;

usar ieee.std_logic_1164.all;

entidade D_flip_flop é

porta (clk,Din,rst,en : em std_logic;

P: fora std_logic;

Qnot: fora std_logic);

fim D_flip_flop;

arquitetura DFF_arch de D_flip_flop é

começar

processo (clk,en,Din,rest)

começar

se(pt='0′) então

Q <='z';

Qnot <= 'z';

elsif(rst='1′) então

Q <='0′;

Qnot <='1′;

elsif(clk'event e clk='1′) então

Q <=Din;

Qnot <= não Din;

fim se;

fim do processo;

fim DFF_arch;

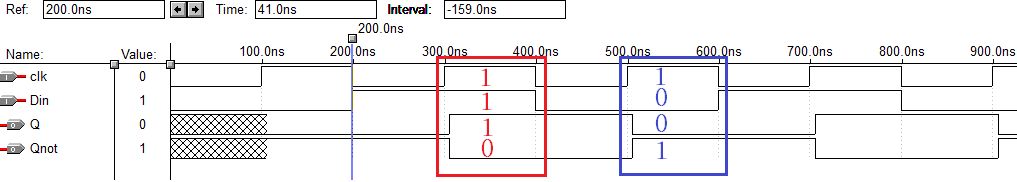

Ao compilar e simular o programa acima, você obterá a seguinte saída em forma de onda…

Formas de onda de simulação

Conforme mostrado nesta figura, há três casos destacados em vermelho, azul e verde.

- Caso 1: quando en = 0, ambas as saídas Q e Qnot são de alta impedância (z)

- Caso 2: quando en=1 e rst=1 -> Q=0 e Qnot=1 (o flip-flop é redefinido)

- Caso 3: quando en=1, rst=0 e Din=1 -> Q=1 e Qnot=0

No próximo tutorial construiremos um circuito flip-flop JK usando VHDL.