Em tutorial anterior Tutorial VHDL 3, aprendemos como projetar, simular e verificar qualquer circuito digital em VHDL usando o software simulador VHDL MAX+II da Altera.

(Se você não estiver seguindo esta série de tutoriais VHDL um por um, será solicitado que você passe por todos os tutoriais anteriores desta série antes de prosseguir neste tutorial)

Neste tutorial,

- Escreveremos um programa VHDL para construir todas as portas digitais

- Simule o programa para projetar circuito digital para todas as portas

- Verifique a forma de onda de saída do programa (circuito digital) com a tabela verdade destes GATES lógicos

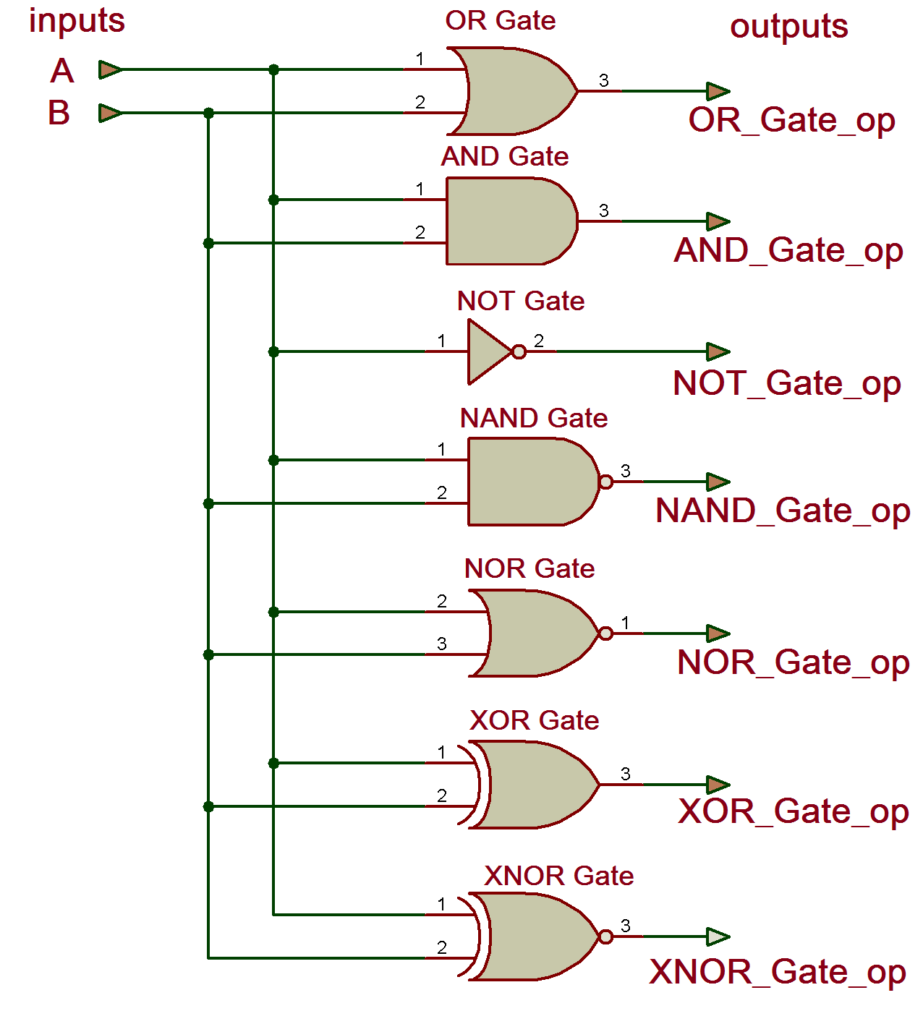

Comecemos com o circuito digital para o qual escreveremos um programa VHDL

Circuito Digital

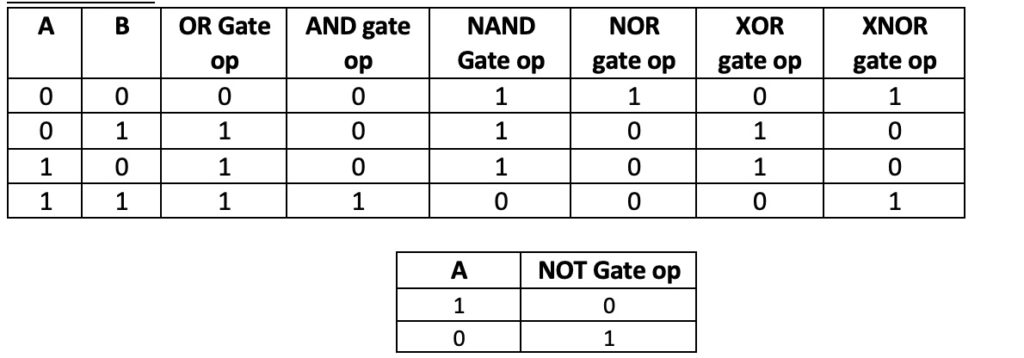

Aqui está a tabela verdade para o circuito acima.

Aqui está a tabela verdade para o circuito acima.

Tabela Verdade

Agora vamos escrever um programa VHDL, compilá-lo, simulá-lo e obter a saída na forma de forma de onda. Por fim, verificaremos essas formas de onda de saída com a tabela verdade fornecida.

Agora vamos escrever um programa VHDL, compilá-lo, simulá-lo e obter a saída na forma de forma de onda. Por fim, verificaremos essas formas de onda de saída com a tabela verdade fornecida.

(Por favor, siga o procedimento passo a passo fornecido no tutorial anterior (Tutorial VHDL 2) para criar um projeto, editar e compilar um programa, criar um arquivo de forma de onda, simular o programa e gerar formas de onda de saída.)

Programa VHDL

biblioteca IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entidade logic_gate é

Porta (A,B: em std_logic;

y_and,y_or,y_nand,y_nor,y_not,y_xor,y_xnor : fora std_logic);

fim portão_lógico;

arquitetura all_gates de logic_gate é

começar

y_and <= a e b;

y_ou <= a ou b;

y_nand <= a nand b;

y_nor <= a nem b;

y_not <= não é um;

y_xor <= a xor b;

y_xnor <= a xnor b;

terminar todos_gates;

“entidade”Descreve as conexões de entrada-saída do circuito digital. De acordo com nosso circuito fornecido acima, temos apenas duas entradas ‘A’ e ‘B’ e 7 saídas para 7 portas.

“arquitetura”descreve a operação do circuito – significa como a saída é gerada a partir de uma determinada entrada.

(Para saber mais e obter mais detalhes sobre o(s) programa(s) VHDL, leia os dois primeiros tutoriais Tutorial 1 de VHDL e Tutorial 2 de VHDL desta série.)

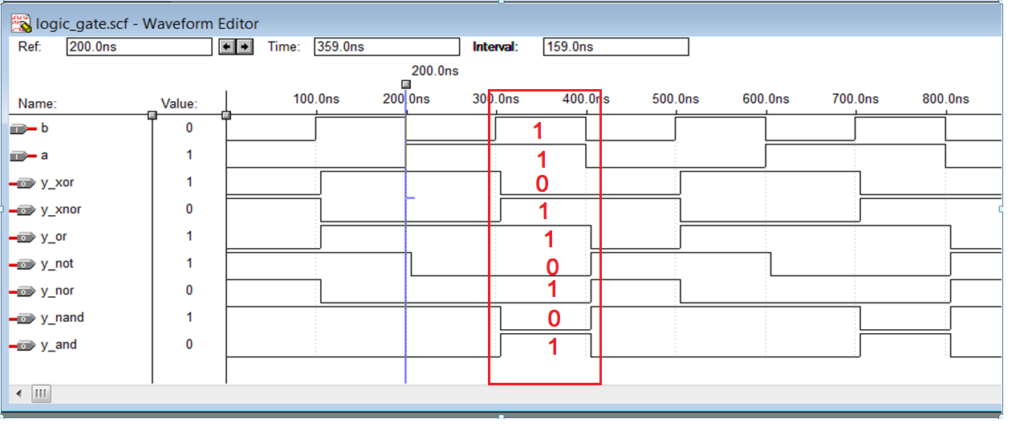

A seguir, compile o programa acima – crie um arquivo de forma de onda com todas as entradas e saídas listadas – simule o projeto e você obterá o seguinte resultado:

Forma de onda de simulação

Agora verifique essas formas de onda de saída com a tabela verdade dos GATEs. Por exemplo, aqui, um caso é destacado com entradas A=1 e B=1. Você também pode verificar os outros três casos.

Agora verifique essas formas de onda de saída com a tabela verdade dos GATEs. Por exemplo, aqui, um caso é destacado com entradas A=1 e B=1. Você também pode verificar os outros três casos.

É assim que você pode construir um circuito lógico GATE simples em VHDL e verificar sua saída com sua tabela verdade.

No próximo tutorialveremos como construir portas NAND, NOR, XOR e XNOR usando três portas básicas AND, OR e NOT usando VHDL.