Nota: é recomendado seguir esta série de tutoriais VHDL em ordem, começando com o primeiro tutorial.

No tutorial anterior Tutorial VHDL – 11aprendemos como projetar circuitos meio subtratores e subtratores completos usando VHDL.

Neste tutorial, iremos:

- Escreva um programa VHDL para construir um gerador de paridade de 8 bits e circuitos verificadores

- Verifique a forma de onda de saída do programa (como um circuito digital) com a tabela verdade do gerador de paridade e dos circuitos verificadores de paridade

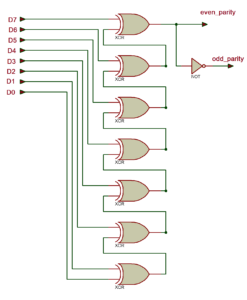

O circuito gerador de paridade de 8 bits

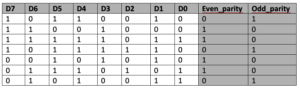

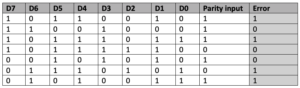

Tabela verdade

Nota: aqui nem todas as 256 combinações do D0-D7 são exibidas. Apenas alguns são tomados como exemplos.

Agora, vamos escrever, compilar e simular um programa VHDL para obter uma saída em forma de onda. Em seguida, verificaremos a saída da forma de onda com a tabela verdade fornecida.

Antes de começar, certifique-se de revisar o procedimento passo a passo fornecido em Tutorial VHDL – 3 projetar adequadamente o projeto, bem como editar e compilar o programa e o arquivo de forma de onda, incluindo a saída final.

Programa VHDL

biblioteca ieee;

use ieee.std_logic_1164.all;

paridade de entidade é

porta(dados:in bit_vector(7 até 0);

par_p,odd_p: bit de saída);

paridade final;

arquitetura parity_gen de paridade é

temperatura do sinal: bit_vector (5 até 0);

começar

temp(0)<=dados(0) xor dados(1);

temp(1)<=temp(0) xor dados(2);

temp(2)<=temp(1) xor dados(3);

temp(3)<=temp(2) xor dados(4);

temp(4)<=temp(3) xor dados(5);

temp(5)<=temp(4) xor dados(6);

par_p <= temp(5) xor dados(7);

estranho_p <= not(temp(5) xor dados(7));

fim paridade_gen;

Observação:

- A “entidade” descreve as conexões de entrada-saída do circuito digital. De acordo com o circuito fornecido aqui, há uma entrada de dados de 8 bits de 'd0-d7' e duas saídas de 'even_p' e 'odd_p.'

- A “arquitetura” descreve a operação do circuito, o que significa como a saída é gerada a partir de uma determinada entrada.

Para refrescar sua memória sobre como isso funciona, leia os dois primeiros tutoriais de VHDL (1 e 2) desta série.

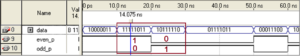

A seguir, compile o programa acima, criando um arquivo de forma de onda com todas as entradas e saídas necessárias listadas, e simule o projeto. Você deve obter o seguinte resultado…

Verifique as formas de onda de saída 'even_p' e 'odd_p' com os dados de entrada de 'D0-D7.' Por exemplo, conforme destacado no diagrama, para a entrada “1111 1011”, a saída par_p é '1' e a saída _p ímpar é '0.' Para a entrada “1011 1110”, a saída par_p é '0' e a saída ímpar_p é '1.'

Agora, vamos construir o circuito verificador de paridade de 8 bits.

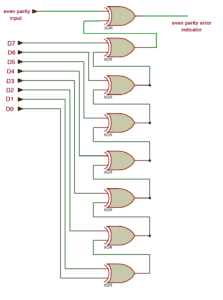

O circuito verificador de paridade de 8 bits

Tabela verdade

Programa VHDL

biblioteca ieee;

use ieee.std_logic_1164.all;

entidade parity_chk é

porta(dados:in bit_vector(7 até 0);

p: em bits;

e: fora do bit);

fim paridade_chk;

arquitetura parity_arch de parity_chk é

temperatura do sinal: bit_vector (6 até 0);

começar

temp(0)<=dados(0) xor dados(1);

temp(1)<=temp(0) xor dados(2);

temp(2)<=temp(1) xor dados(3);

temp(3)<=temp(2) xor dados(4);

temp(4)<=temp(3) xor dados(5);

temp(5)<=temp(4) xor dados(6);

temp(6) <= temp(5) xor dados(7);

e <= p xor temp(6);

fim paridade_arch;

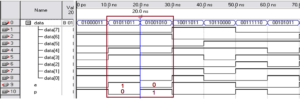

Formas de onda de simulação

Verifique a forma de onda de saída 'e' com a entrada de paridade de 'p' e os dados 'D0-D7.' Por exemplo, conforme destacado no diagrama, para a entrada “0101 1011” e a paridade '1', a saída de erro é '1.' Para a entrada “0100 1010” e a paridade '0', a saída é '0.'

No próximo tutorial, aprenderemos como projetar circuitos codificadores 8×3 e decodificadores 3×8 usando VHDL.