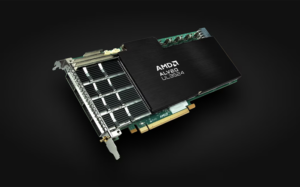

AMD anunciou a placa aceleradora AMD Alveo UL3524, um novo acelerador fintech projetado para aplicações de negociação eletrônica de latência ultrabaixa. Já implementado pelas principais empresas de negociação e permitindo múltiplas ofertas de soluções de parceiros, o Alveo UL3524 fornece aos comerciantes proprietários, formadores de mercado, fundos de hedge, corretoras e bolsas uma plataforma FPGA de última geração para negociação eletrônica em velocidade de nanossegundos (ns). .

O Alveo UL3524 oferece uma melhoria de latência de 7X em relação à tecnologia FPGA da geração anterior, alcançando menos de 3ns de latência do transceptor FPGA para execução acelerada de negociações. Alimentado por um Virtex UltraScale + FPGA personalizado de 16 nm, ele apresenta uma nova arquitetura de transceptor com núcleos de conectividade de rede otimizados e reforçados para alcançar um desempenho inovador.

O Alveo UL3524 oferece uma melhoria de latência de 7X em relação à tecnologia FPGA da geração anterior, alcançando menos de 3ns de latência do transceptor FPGA para execução acelerada de negociações. Alimentado por um Virtex UltraScale + FPGA personalizado de 16 nm, ele apresenta uma nova arquitetura de transceptor com núcleos de conectividade de rede otimizados e reforçados para alcançar um desempenho inovador.

Ao combinar flexibilidade de hardware com rede de latência ultrabaixa em uma plataforma de produção, o Alveo UL3524 permite fechamento e implantação de projeto mais rápidos em comparação com alternativas tradicionais de FPGA.

“Na negociação de latência ultrabaixa, um nanossegundo pode determinar a diferença entre uma negociação lucrativa ou perdedora”, disse Hamid Salehi, diretor de marketing de produto da AMD. “A placa aceleradora Alveo UL3524 é alimentada pelo transceptor FPGA de menor latência da AMD – desenvolvido especificamente para oferecer aos nossos clientes fintech uma vantagem competitiva sem precedentes nos mercados financeiros.”

Estratégias de negociação habilitadas para IA

Apresentando 64 transceptores de latência ultrabaixa, 780K LUTs de estrutura FPGA e 1.680 fatias DSP de computação, o Alveo UL3524 foi desenvolvido para acelerar algoritmos de negociação personalizados em hardware, onde os traders podem adaptar seu design às estratégias e condições de mercado em evolução.

Suportado por fluxos FPGA tradicionais usando o Vivado Design Suite, o produto vem com um conjunto de designs de referência e benchmarks de desempenho que permitem aos projetistas de FPGA explorar rapidamente as principais métricas e desenvolver estratégias de negociação personalizadas de acordo com as especificações, apoiadas pelo suporte global de especialistas no domínio da AMD.

Para simplificar a crescente adoção de IA no mercado de negociação algorítmica, a AMD está fornecendo aos desenvolvedores a estrutura de desenvolvimento FINN de código aberto e apoiada pela comunidade. Ao usar técnicas de quantização de redes neurais e PyTorch, o projeto FINN permite que os desenvolvedores reduzam o tamanho dos modelos de IA, mantendo a precisão, compilando para IP de hardware e integrando o modelo de rede no caminho de dados do algoritmo para desempenho de baixa latência. Como uma iniciativa de código aberto, a solução oferece aos desenvolvedores flexibilidade e acessibilidade aos avanços mais recentes à medida que os projetos evoluem.

Soluções fintech de latência ultrabaixa

O Alveo UL3524 e a tecnologia FPGA desenvolvida especificamente estão permitindo que parceiros estratégicos construam soluções e infraestrutura personalizadas para o mercado fintech. As soluções de parceiros atualmente disponíveis incluem ofertas da Alpha Data, Exegy e Hypertec.

O FPGA AMD Virtex UltraScale+ VU2P que alimenta a placa aceleradora Alveo UL3524 está habilitando dispositivos de latência ultrabaixa da Alpha Data.

“O novo Virtex UltraScale+ FPGA da AMD traz uma mudança radical para negociação e rede de latência ultrabaixa”, disse David Miller, diretor administrativo da Alpha Data. “Desenvolvemos o dispositivo de montagem em rack ADA-R9100 que permite aos clientes acessar facilmente todo o potencial do novo dispositivo AMD FPGA.”

A Exegy, fornecedora de soluções de negociação de front-office ponta a ponta, está oferecendo suporte à placa Alveo UL3524 com seu nxFramework, um ambiente de desenvolvimento de software e hardware adaptado para criar e manter aplicações FPGA de latência ultrabaixa no setor financeiro.

“Ao combinar a tecnologia pioneira FPGA de latência ultrabaixa da AMD com a experiência da Exegy em mercados de capitais, somos capazes de fornecer uma solução abrangente que aborda a otimização cada vez maior necessária para construir a infraestrutura comercial de amanhã”, disse Olivier Cousin, diretor de soluções FPGA da Exegy.

A Hypertec otimizou seu servidor de alta frequência ORION HF X410R-G6 para o Alveo UL3524 com um sistema de resfriamento personalizado para implantação em um formato de servidor 1U.

“Os engenheiros da Hypertec projetaram especificamente o HF X410R-G6 para extrair o melhor dos recursos e da velocidade da plataforma Alveo UL3524, atendendo nossa solução às tarefas mais exigentes de baixa latência”, disse David Lim, diretor de marketing de produto, Hipertec.

A placa aceleradora AMD Alveo UL3524 está atualmente em produção e sendo enviada para clientes globais de serviços financeiros.