Nota: é recomendado seguir esta série de tutoriais VHDL em ordem, começando com o primeiro tutorial.

No tutorial anterior, Tutorial VHDL – 20aprendemos como projetar conversores de código binário para cinza e cinza para binário de 4 bits usando VHDL.

Neste tutorial, iremos:

- Escreva um programa VHDL que construa um circuito somador completo de 8 bits

- Verifique a forma de onda de saída do programa (o circuito digital) com a operação do circuito

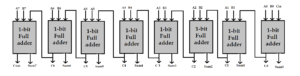

O diagrama de blocos de somador completo de 8 bits:

Agora vamos escrever, compilar e simular um programa VHDL. Então, obteremos a saída da forma de onda e a verificaremos.

Agora vamos escrever, compilar e simular um programa VHDL. Então, obteremos a saída da forma de onda e a verificaremos.

Antes de começar, certifique-se de revisar o procedimento passo a passo fornecido em Tutorial VHDL – 3 para elaborar o projeto. Isso garantirá que você edite e compile corretamente o programa e o arquivo de forma de onda, bem como a saída final.

Para este projeto, usamos um estilo de modelagem estrutural para construir o circuito somador completo de 8 bits. Um somador completo de 1 bit é usado como componente.

Programa VHDL

biblioteca ieee;

use ieee.std_logic_1164.all;

entidade FA_8bit é

porta(x,y: em std_logic_vector(7 até 0);

cin: em std_logic;

soma: out std_logic_vector(7 até 0);

co: saída std_logic);

fim FA_8bit;

arquitetura FA_arch de FA_8bit é

sinal cary: std_logic_vector (6 até 0);

componente full_adder é

porta (p,q,r:in std_logic; sm,cr:out std_logic);

componente final;

começar

a0:mapa de porta full_adder (x(0),y(0),cin,sum(0),cary(0));

a1:mapa de porta full_adder (x(1),y(1),cary(0),sum(1),cary(1));

a2:mapa de porta full_adder (x(2),y(2),cary(1),sum(2),cary(2));

a3:mapa de porta full_adder (x(3),y(3),cary(2),sum(3),cary(3));

a4:mapa de porta full_adder (x(4),y(4),cary(3),sum(4),cary(4));

a5:mapa de porta full_adder (x(5),y(5),cary(4),sum(5),cary(5));

a6:mapa de porta full_adder (x(6),y(6),cary(5),sum(6),cary(6));

a7:mapa de porta full_adder (x(7),y(7),cary(6),sum(7),co);

fim FA_arch;

biblioteca ieee;

use ieee.std_logic_1164.all;

entidade full_adder é

porta (p,q,r:in std_logic; sm,cr:out std_logic);

fim completo_adder;

arquitetura FA_arc de full_adder é

começar

sm <= p xor q xor r;

cr <= (p e q) ou (q e r) ou (r e p);

fim FA_arc;

Pode ser útil revisar os dois primeiros tutoriais de VHDL (1 e 2) desta série para refrescar sua memória sobre como isso funciona.

Em seguida, compile o programa acima, criando e salvando um arquivo de forma de onda com todas as entradas e saídas necessárias listadas (garantindo a aplicação de todas as diferentes combinações de entrada). Em seguida, simule o projeto. Você deve obter o seguinte resultado…

Forma de onda de simulação

Como pode ser observado nesta figura, a soma de x, y e cin estão destacadas em vermelho e azul.

No próximo tutorial, aprenderemos como projetar um comparador digital usando VHDL.