No tutorial anterior do tutorial VHDL, projetamos circuitos codificadores 8×3 e decodificadores 3×8 usando VHDL.

(Se você não estiver seguindo esta série de tutoriais VHDL um por um, será solicitado que você passe por todos os tutoriais anteriores desta série antes de prosseguir neste tutorial)

Neste tutorial,

- Escreveremos um programa VHDL para construir circuitos demultiplexadores 1×8 e multiplexadores 8×1

- Verifique a forma de onda de saída do programa (circuito digital) com a tabela verdade desses circuitos multiplexadores e demultiplexadores

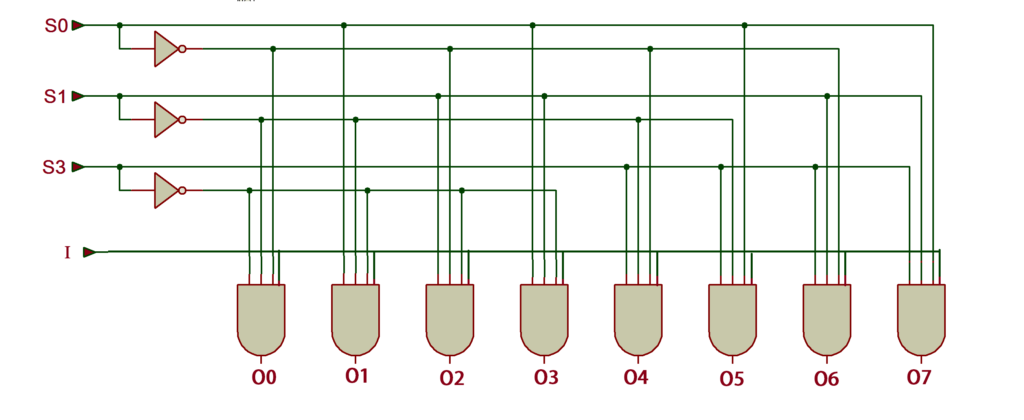

Circuito Demultiplexador 1×8

Tabela Verdade

(Por favor, siga o procedimento passo a passo fornecido no tutorial VHDL 3 para criar um projeto, editar e compilar o programa, criar um arquivo de forma de onda, simular o programa e gerar formas de onda de saída.)Agora vamos escrever um programa VHDL, compilá-lo, simulá-lo e obter a saída em forma de onda. Por fim, verificaremos se as formas de onda de saída estão de acordo com a tabela verdade fornecida.

Usei o estilo de modelagem comportamental para escrever um programa VHDL para construir o demultiplexador porque será mais fácil do que o estilo de fluxo de dados ou de modelagem estrutural.

Programa VHDL

(Para saber mais e obter mais detalhes sobre o(s) programa(s) VHDL, leia os dois primeiros tutoriais, Tutorial VHDL 1 e Tutorial VHDL 2 desta série.)

Em seguida, compile o programa acima – crie um arquivo de forma de onda com todas as entradas e saídas listadas – aplique diferentes combinações de entrada – salve o arquivo de forma de onda e, finalmente, simule o projeto. Você obterá o seguinte resultado.

Simulação de forma de onda

Conforme mostrado na figura, pode-se observar que quando as linhas selecionadas (S2, S1, S0) são “001”, a entrada I=0 está disponível na saída O1=0, e quando as linhas selecionadas são “101”, a entrada I =1 está disponível na saída O5 = 1. Você pode verificar outras combinações de linhas selecionadas com entrada e saída.

A seguir, vamos construir um circuito multiplexador 8×1.

Circuito multiplexador 8×1

Tabela verdade

Programa VHDL

Formas de onda de simulação

Formas de onda de simulação

Conforme mostrado na figura, pode-se observar que para as linhas selecionadas (S2, S1, S0) “011” e “100”, as entradas d3=1 e d4=1 estão disponíveis na saída o=1. Você pode verificar outras combinações de linhas selecionadas da tabela verdade.

No próximo tutorial, projetaremos o flip-flop RS e o RS Latch com clock.