Nota: é recomendado seguir esta série de tutoriais VHDL em ordem, começando com o primeiro tutorial.

No tutorial anterior Tutorial VHDL – 10projetamos circuitos meio somadores e completos usando VHDL.

Neste tutorial, iremos:

- Escreva um programa VHDL para construir circuitos meio subtratores e subtratores completos

- Verifique a forma de onda de saída do programa (circuito digital) com as tabelas verdade para os circuitos meio subtrator e completo

Circuito meio subtrator

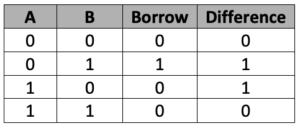

Tabela verdade

Agora, vamos escrever, compilar e simular um programa VHDL para obter uma saída em forma de onda. Em seguida, verificaremos a saída da forma de onda com a tabela verdade fornecida.

Antes de começar, certifique-se de revisar o procedimento passo a passo fornecido em Tutorial VHDL – 3 projetar adequadamente o projeto, bem como editar e compilar o programa e o arquivo de forma de onda, incluindo a saída final.

Programa VHDL:

biblioteca IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entidade half_sub é

porta (a,b: em std_logic;

dif,bo: saída std_logic

);

fim half_sub;

arquitetura sub_arch de half_sub é

começar

dif <= a x ou b;

bo <= (não a) eb;

final sub_arca;

Observação:

- A “entidade” descreve as conexões de entrada-saída do circuito digital. De acordo com o circuito fornecido aqui, você notará que existem duas entradas ('a' e 'b') e duas saídas ('dif' e 'bo').

- A “arquitetura” descreve a operação do circuito, o que significa como a saída é gerada a partir de uma determinada entrada.

Para refrescar sua memória sobre como isso funciona, leia os dois primeiros tutoriais de VHDL (1 e 2) desta série.

A seguir, compile o programa acima, criando um arquivo de forma de onda com todas as entradas e saídas necessárias listadas, e simule o projeto. Você deve obter o seguinte resultado…

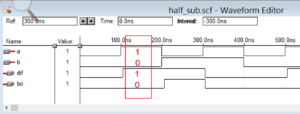

Forma de onda de simulação

Verifique as formas de onda de saída 'dif' e 'bo' com a tabela verdade fornecida. Para entradas a=1 e b=0, as saídas são bo=0 e dif=1, que estão destacadas na imagem.

A seguir, vamos passar para o circuito subtrator completo e seu design.

Circuito subtrator completo

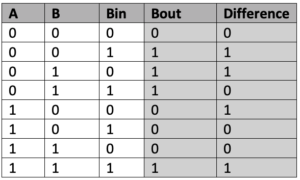

Tabela verdade

Vamos escrever o programa VHDL para este circuito. No tutorial anterior, projetamos o circuito somador completo usando um estilo de modelagem estrutural para a programação VHDL. Usaremos o mesmo estilo de modelagem para projetar o subtrator completo.

Construiremos o circuito subtrator completo usando o circuito meio subtrator e o “OU portão”Como componentes (ou blocos). No diagrama de circuito você pode ver que o circuito subtrator completo consiste em dois meio somadores e uma porta OR.

Programa VHDL

biblioteca IEEE;

Utilize o IEEE. STD_LOGIC_1164.all;

entidade full_sub IS

porta (a,b,bin:em STD_LOGIC;

dif,bout : out STD_LOGIC);

fim full_sub;

———————–arquitetura do subtrator completo ————-

arquitetura FS_arch de full_sub é

—————————–meio componente somador————————–

componente half_sub é

porta (p,q :em STD_LOGIC;

dif,bo: saída STD_LOGIC);

componente final;

———————ou componente de portão ————————-

componente or_gate é

porta (p1,q1:em STD_LOGIC;

r1: saída STD_LOGIC);

componente final;

—————————-

sinal d1,b1,b2: STD_LOGIC;

começar

w1: mapa de porta half_sub (a,b,d1,b1);

w2: mapa de porta half_sub (d1,bin,dif,b2);

w3: mapa da porta or_gate (b1,b2,bout);

fim FS_arch;

————————– programa meio subtrator ————————

biblioteca IEEE;

Utilize o IEEE. STD_LOGIC_1164.all;

entidade half_sub é

porta (p,q: em STD_LOGIC;

dif,bo : saída STD_LOGIC);

fim half_sub;

arquitetura HS_arch de half_sub IS

começar

dif <= p xor q;

bo <= (não p) e q;

fim HS_arch;

—————————–ou programa de portão ——————————

biblioteca IEEE;

Utilize o IEEE. STD_LOGIC_1164.all;

entidade ou_gate é

porta (p1,q1:em STD_LOGIC;

r1: saída STD_LOGIC);

fim ou_gate;

arquitetura or_g de or_gate IS

começar

r1 <= p1 ou q1;

fim or_g;

Para compilar o programa acima:

- Crie o arquivo de forma de onda com todas as entradas e saídas listadas

- Aplique as diferentes combinações de entrada

- Salve o arquivo de forma de onda e simule o projeto

Você deve obter este resultado…

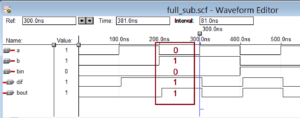

Formas de onda de simulação

Compare os resultados de 'dif' e 'bout' com a tabela verdade fornecida. No diagrama acima, um caso é destacado como a=0, b=1 e bin=0 com as saídas de dif=1 e bout=1.

No próximo tutorial, aprenderemos como projetar um gerador de paridade de 8 bits e circuitos verificadores de paridade usando VHDL.