SPI conquistou um papel sólido em sistemas embarcados, sejam processadores de sistema em chip, tanto com processadores de 32 bits de última geração, como aqueles que usam ARM, MIC ou Power PC, quanto com outros microcontroladores, como AVR, PIC etc. incluem controladores SPI capazes de funcionar em modo mestre ou escravo. Os controladores AVR programáveis no sistema podem ser programados usando uma interface SPI. Projetos baseados em chip ou FPGA às vezes usam SPI para se comunicar. Assim, SPI é uma tecnologia comum utilizada hoje em dia para comunicação com dispositivos periféricos onde queremos transferir dados de forma rápida e com restrições em tempo real. Existem muitas interfaces seriais desde telegrafia em código Morse, RS232, USB, Fire wire, Ethernet e muito mais. Cada interface serial oferece vantagens ou desvantagens para muitos projetos, dependendo de critérios como taxa de dados necessária, disponibilidade de espaço e considerações de ruído.

Interface serial para periférico (SPI) foi uma dessas tecnologias desenvolvidas para substituir interfaces paralelas, para que não tenhamos que rotear o barramento paralelo em torno do PCB. Ele fornece transferência de dados em alta velocidade entre os dispositivos. A Motorola foi a primeira empresa a nomear SPI para uma técnica de circuito usada no final da década de 1970 em seu primeiro MCU baseado em 68000 para conectá-lo a funções periféricas e posteriormente adotado por outros na indústria. É a simplicidade da interface e a velocidade que permite a comunicação ou transferência de dados facilmente e o tornou um protocolo de comunicação popular.

A Interface Periférica Serial é uma interface de comunicação serial simples de 4 fios usada por muitos chips periféricos de microprocessadores/microcontroladores que permite que os controladores e dispositivos periféricos se comuniquem entre si. Na interface periférica serial, os dados são transferidos para dentro/para fora um de cada vez e transmitem dados do dispositivo mestre para/de um ou mais dispositivos escravos em distâncias curtas e alta velocidade. É simplesmente baseado em um registrador de deslocamento de 8 bits que transfere dados para um único pino e transfere dados para outro pino. Outra característica do SPI é que não existe o conceito de transferência de propriedade do barramento, ou seja, troca do mestre e também não há endereços de escravos. O SPI é um protocolo muito mais simples e por isso podemos operá-lo em velocidades superiores a 10MH em comparação ao TWI. Alguns dos recursos que permitem o SPI amplamente utilizado são-

1. Comunicação full duplex.

2. Maior rendimento que o TWI.

3. Não limitado a palavras de 8 bits no caso de transferência de bits.

4. Interface de hardware simples

5. Escolha arbitrária de tamanho, conteúdo e finalidade das mensagens.

6. Requisitos de energia normalmente baixos

7. O escravo usa relógio mestre e não requer osciladores de precisão.

8. Requisitos de energia mais baixos do que o TWI devido a menos circuitos.

No entanto, seria injusto comparar a interface serial TWI com a SPI. Cada um deles tem sua área de aplicação dependendo da necessidade do sistema, como alguns dos recursos que tornam o TWI tão valioso quanto o SPI.

1. Menor número de pinos em pacotes IC do que SPI

2. O controle de fluxo de hardware está presente

3. Possui um padrão formal diferente do SPI

4. Aborda os escravos antes da comunicação.

Agora que temos uma breve ideia sobre SPI, vamos entender as respostas às perguntas sobre por que o SPI é mais preferido em PCB? Quais são as conexões básicas e como elas se comunicam? E por último qual é o escopo futuro do SPI?

Por que o SPI é mais preferido para PCB

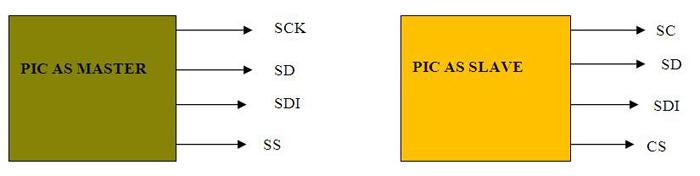

Figura 1: Imagem de bloco mostrando o funcionamento do protocolo SPI

Embora tenha sido desenvolvido principalmente para a comunicação entre o processador host e os periféricos, uma conexão de dois processadores via SPI também é possível. O barramento SPI geralmente é usado apenas no PCB. Existem muitos motivos que nos impedem de utilizá-lo fora da área de PCB. Primeiramente, o SPI foi projetado para transferir dados entre vários chips IC, em velocidades muito altas. Devido a esta alta velocidade o comprimento das linhas do barramento não deve ser muito longo, pois aumenta a reatância e o barramento fica inutilizável. Porém, é possível usar o barramento SPI fora da placa de circuito impresso em baixas velocidades, mas isso não é muito prático. Os periféricos podem ser relógios de tempo real, conversores como ADC e DAC, módulos de memória como EEPROM e FLASH, sensores como sensores de temperatura e sensores de pressão, ou alguns outros dispositivos como misturador de sinal, potenciômetro, controlador LCD, UART, controlador CAN, USB controlador e amplificador.

Linhas de dados e controle do SPI e conexão básica:

Um protocolo SPI especifica 4 fios de sinal.

1. Master Out Slave In (MOSI) – O sinal MOSI é gerado pelo Master, o destinatário é o Slave.

2. Master In Slave Out (MISO) – Os escravos geram sinais MISO e o destinatário é o Mestre.

3. Relógio serial (SCLK ou SCK) – O sinal SCLK é gerado pelo Mestre para sincronizar as transferências de dados entre o mestre e o escravo.

4. Seleção de escravo (SS) do mestre para seleção de chip (CS) do escravo – o sinal SS é gerado pelo mestre para selecionar dispositivos escravos/periféricos individuais. O SS/CS é um sinal baixo ativo.

Às vezes, serial Data In (SDI) é usado como outro nome no lugar de MOSI e Serial Data Out (SDO) para MISO.

Figura 2: Diagrama de blocos mostrando aplicação mestre único mestre único no protocolo SPI

Dentre esses quatro sinais lógicos, dois deles MOSI e MISO podem ser agrupados como linhas de dados e outros dois SS e SCLK como linhas de controle.

Um microcontrolador mestre pode se comunicar com vários periféricos SPI. Existem 2 maneiras de configurar as coisas:

1. Escravos em cascata ou escravos encadeados

2. Escravos independentes ou configuração paralela

Configuração de escravo em cadeia

Configuração de escravo em cadeia: Na configuração de escravo em cascata, todas as linhas de clock (SCLK) e seleção de chip (CS) são conectadas juntas. Os dados fluem do microcontrolador para cada periférico e voltam para o microcontrolador. A saída de dados do dispositivo escravo anterior está ligada à entrada de dados do próximo, formando assim um registrador de deslocamento mais amplo. Assim, os dispositivos escravos em cascata são evidentemente vistos como um dispositivo maior e recebem, portanto, o mesmo sinal de seleção de chip. Isto significa que apenas uma única linha SS é necessária do mestre, em vez de uma linha SS separada para cada escravo.

Figura 3: Configuração de escravo em cadeia no protocolo SPI

Mas devemos lembrar que o encadeamento em série não funcionará com dispositivos que suportam ou exigem operação de múltiplos bytes.

Configuração de escravo independente:

Esta é a configuração típica do barramento SPI com um mestre SPI e vários escravos/periféricos. Nesta configuração de escravo independente ou paralelo,

Todas as linhas de clock (SCLK) estão conectadas entre si.

2. Todas as linhas de dados MISO estão conectadas entre si.

3. Todas as linhas de dados MOSI estão conectadas entre si.

Figura 4: Diagrama de blocos exibindo o barramento SPI na configuração escravo

Figura 5: Diagrama de blocos mostrando várias unidades funcionais no sistema SPI

Comunicação no SPI

Como funciona a comunicação no SPI?

A comunicação é iniciada pelo mestre o tempo todo. O mestre primeiro organiza o relógio usando uma frequência menor ou igual à frequência máxima suportada pelo dispositivo escravo. Agora, este mestre SPI controla a transferência de dados gerando o sinal de clock (SCLK). O mestre então seleciona o escravo desejado para comunicação puxando a linha de seleção de chip (SS) daquele periférico escravo específico para o estado “baixo” e ativa o determinado escravo com o qual deseja se comunicar usando o sinal de seleção de escravo (SS). Uma vez selecionado o escravo, ele recebe ou transmite dados através das duas linhas de dados. Um mestre, geralmente o microcontrolador host, sempre fornece sinal de clock para todos os dispositivos em um barramento, esteja ele selecionado ou não. Os escravos no barramento que não foram ativados pelo mestre usando seu sinal de seleção de escravo desconsiderarão o relógio de entrada e os sinais MOSI do mestre e não deverão acionar MISO. Isso significa que o mestre seleciona apenas um escravo por vez.

O uso de cada quatro pinos pode depender dos dispositivos. Por exemplo, o pino SDI pode não estar presente se um dispositivo não necessitar de uma entrada (ADC, por exemplo), ou o pino SDO pode não estar presente se um dispositivo não necessitar de uma saída (controladores LCD, por exemplo). Se um microcontrolador precisar se comunicar apenas com 1 periférico SPI ou um escravo, então o pino CS desse escravo pode ser aterrado. Com vários dispositivos escravos, é necessário um sinal SS independente do mestre para cada dispositivo escravo.

Qual é a importância da produção Tri-state no SPI?

Na eletrônica digital, a lógica de três estados, três estados ou 3 estados permite que uma porta de saída assuma um estado de alta impedância além dos níveis lógicos 0 e 1, removendo efetivamente a saída do circuito. Isso permite que vários circuitos compartilhem a mesma linha ou linhas de saída (como um barramento que não pode ouvir mais de um dispositivo ao mesmo tempo. A maioria dos dispositivos/periféricos tem saídas de três estados, que vão para o estado de alta impedância (desconectado) quando o dispositivo não está selecionado. Dispositivos sem essas saídas tri-state não podem compartilhar o barramento SPI com outros dispositivos, porque a seleção de chip desse escravo pode não ser ativada.

Agora, se for necessário um período de espera (como para conversão analógico-digital), então o mestre deve esperar pelo menos esse período de tempo antes de começar a emitir ciclos de clock. No SPI mestre, os bits são enviados do pino MOSI e recebidos no pino MISO. Os bits a serem deslocados são armazenados no registrador de dados SPI, SP0DR, e são enviados primeiro o bit mais significativo (bit 7). Quando o bit 7 do mestre é deslocado através do pino MOSI, um bit do bit 7 do escravo é deslocado para o bit 0 do mestre através do pino MISO. Após 8 pulsos ou turnos de clock, esse bit acabará no bit 7 do mestre. O bit menos significativo pode ser enviado primeiro definindo o bit LSBF como 1 no registrador de controle SPI. O clock que controla a rapidez com que os bits são transferidos para SP0DR é o sinal SCLK. A frequência deste clock pode ser controlada pelo registro de taxa de transmissão SPI, SP0BR. O pino SS deve estar baixo para selecionar um escravo. Um sistema SPI completo é mostrado abaixo.

Figura 6: Visão Geral da Comunicação no Sistema SPI com Mestre e Escravo

Figura 7: Diagrama mostrando a estrutura do SPI Slave

Um full duplex significa que a transmissão de dados pode ocorrer em ambas as direções durante cada ciclo de clock. Então, quando o master envia um bit na linha MOSI; o escravo lê dessa mesma linha e o escravo envia um bit na linha MISO; o mestre lê na mesma linha. Agora, para fazer a transferência de dados, registradores de deslocamento organizados são usados com um determinado tamanho de palavra, como 8 bits (pode ser mais) tanto no mestre quanto no escravo. Eles estão conectados em um anel. Enquanto o mestre transfere o valor do registrador através da linha MOSI, o escravo transfere os dados para seu registrador de deslocamento.

Os dados geralmente são deslocados com o bit mais significativo do MSB primeiro, enquanto o novo bit menos significativo do LSB é deslocado para o mesmo registro. Após a mudança desse registro, o mestre e o escravo trocaram seus valores de registro. Então cada dispositivo pega esse valor e faz a operação necessária com ele (por exemplo, gravando-o na memória). Se houver mais dados a serem trocados, os registradores de deslocamento são carregados com novos dados e o processo é repetido. Quando não há mais dados a serem transmitidos, o mestre para o relógio. Normalmente, ele rejeita o escravo.

Figura 8: Diagrama de blocos mostrando configuração de hardware para comunicação entre 2 registros

Existe um “modo de fluxo de bytes múltiplos” disponível com interface de barramento SPI. Neste modo o mestre pode deslocar bytes continuamente. Neste caso, a seleção de escravos (SS) é mantida baixa até que todo o processo de fluxo seja concluído.

Os dispositivos SPI às vezes usam outra linha de sinal para enviar um sinal de interrupção para uma CPU host. Alguns dos exemplos desse tipo de sinal são interrupções de caneta de sensores de tela sensível ao toque, alertas de limite térmico de sensores de temperatura, alarmes emitidos por chips de relógio em tempo real e inserções de conectores de fone de ouvido do codec de som de um telefone celular.

Polaridade e fase do relógio no SPI

Significado da polaridade e fase do relógio:

Outro par de parâmetros denominado polaridade do relógio (CPOL) e fase do relógio (CPHA) determina as bordas do sinal do relógio nas quais os dados são conduzidos e amostrados. Além de configurar a frequência do clock, o mestre também deve configurar meios de ajustar ou definir a polaridade do clock (CPOL) e a fase (CPHA) em relação aos dados. Como o relógio serve para sincronização da comunicação de dados, existem quatro modos possíveis que podem ser utilizados em um protocolo SPI, baseado neste CPOL e CPHA.

|

Modo |

Polaridade do Relógio (CPOL) |

Fase do Relógio (CPHA) |

|

SPI_MODE0 |

0 |

0 |

|

SPI_MODE1 |

0 |

1 |

|

SPI_MODE2 |

1 |

0 |

|

SPI_MODE3 |

1 |

1 |

Fig. 9: Diagrama de temporização de SPI usando VHDL

Se a fase do relógio for zero (ou seja, CPHA = 0), os dados serão travados na borda ascendente do relógio com CPOL = 0 e na borda descendente do relógio com CPOL = 1.

Se CPHA = 1, as polaridades são invertidas. Os dados são travados na borda descendente do relógio com CPOL = 0 e na borda ascendente com CPOL = 1.

Os microcontroladores permitem ajustar a polaridade e a fase do relógio. Uma polaridade positiva resulta no travamento de dados na borda ascendente do relógio. No entanto, os dados são colocados na linha de dados já na borda descendente para se estabilizarem. A maioria dos periféricos, que só podem ser escravos, funcionam com esta configuração. Se for necessário usar a outra polaridade, as transições serão invertidas.

APLICAÇÕES DO SPI

A capacidade full duplex torna o SPI muito eficiente para aplicações mestre/escravo. Alguns dispositivos usam o modo full-duplex para implementar um fluxo de dados rápido e eficiente para aplicações como áudio digital, processamento de sinal digital ou canais de telecomunicações. SPI é usado para se comunicar com vários periféricos, como

Sensores: Temperatura, pressão, ADC, telas sensíveis ao toque, controladores de videogame

Dispositivos de controle: Codificação e decodificação de áudio, potenciômetros digitais, DAC.

Lentes de câmera: montagem de lente Canon EF

Comunicações: Ethernet, USB, USART, videogames portáteis CAN

Memória: Flash e EEPROM

Relógios em tempo real

LCD, às vezes até para gerenciar dados de imagem

Qualquer cartão MMC ou SD (incluindo variante SDIO)

Para sistemas de alto desempenho, os FPGAs às vezes usam SPI para fazer interface como escravo para um host, como mestre para sensores ou para memória flash usada para inicialização, se forem baseados em SRAM.

JTAG é essencialmente uma pilha de aplicativos para um tipo SPI de três fios, usando nomes de sinais diferentes. SGPIO é essencialmente outra pilha de aplicativos (incompatível) para SPI projetada para atividades específicas de gerenciamento de backplane. SGPIO usa mensagens de 3 bits.