No tutorial anterior, foi discutido como operações aritméticas em números binários podem ser implementadas por meio de operações lógicas booleanas. Num circuito digital, as operações lógicas são executadas por portas lógicas. Uma porta lógica é um circuito eletrônico que toma decisões lógicas. O AND, OR e NOT são as portas lógicas básicas.

As portas NAND e NOR são derivadas delas. Qualquer problema de computação em circuitos digitais pode ser expresso por uma equação booleana ou expressão booleana. Uma expressão booleana pode ser minimizada para Minterms ou Maxterms, reduzindo a expressão para uma implementação de dois níveis que pode ser projetada com portas NAND ou NOR. É por isso que as portas NAND e NOR são chamadas de portas universais. As portas OR exclusivas são outra porta lógica que pode ser construída usando portas básicas, como portas OR e NOT.

As portas lógicas podem ter duas ou mais entradas e apenas uma saída esperada para a porta NOT, que possui apenas uma entrada. O sinal de saída de uma porta lógica aparece apenas para certas combinações dos sinais de entrada, pois o número de combinações é sempre limitado pelo número de variáveis booleanas (onde cada variável booleana representa um canal de entrada).

Então, basicamente, as portas lógicas são os blocos de construção de um circuito digital que pode realizar a manipulação básica da informação binária. Qualquer IC digital contém nada além de uma rede interconectada de portas lógicas. Cada porta é representada por um símbolo lógico distinto e seu funcionamento pode ser descrito por meio de uma função algébrica. A relação entre as variáveis de entrada e saída de cada porta pode ser representada por meio de uma tabela verdade e a resposta do sinal de qualquer porta lógica pode ser representada pelo diagrama de temporização. Então, vamos aprender sobre várias portas lógicas.

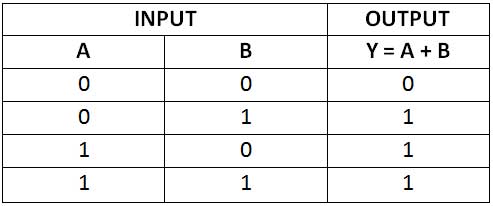

OU Portão –

A porta OR realiza adição lógica, comumente conhecida como função OR. A porta OR possui duas ou mais entradas e apenas uma saída. A operação da porta OR é tal que HIGH (1) na saída é produzido quando qualquer uma das entradas é HIGH (1). A saída é BAIXA (0) somente quando todas as entradas são BAIXAS (0). Suponha que, se A e B são as variáveis de entrada de uma porta OR e Y é sua saída, então

S = A + B

Da mesma forma, para mais de duas variáveis de entrada, a saída da porta OR pode ser expressa da seguinte forma –

Y = A + B + C + D +……

Uma porta OR construída com diodos é mostrada abaixo, na qual A e B representam as entradas e Y a saída. A resistência RL é a resistência da carga. O símbolo lógico da porta OR também é mostrado abaixo –

Fig. 1: Imagem mostrando o símbolo e circuito da porta OR

Se A = 0 e B = 0, ambos os diodos não conduzirão, portanto a saída Y = 0. Se A = 1 e B = 0, o diodo D1 conduz, portanto a saída Y = 1. Se A = 0 e B = 1, o diodo D2 conduz, portanto a saída Y = 1. Se A = 1 e B = 1, ambos os diodos conduzem e, portanto, Y = 1. A saída de uma porta OR para duas variáveis booleanas pode ser representada pela seguinte tabela verdade –

Figura 2: Tabela verdade da porta OR

A tabela verdade para a porta OR pode ser representada graficamente pelo seguinte diagrama de tempo –

Fig. 3: Diagrama de temporização da porta OR

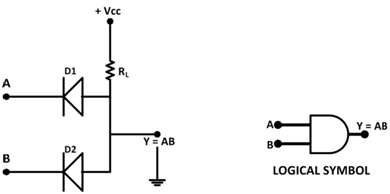

E Portão –

A porta AND realiza multiplicação lógica, comumente conhecida como função AND. A porta AND possui duas ou mais entradas e uma única saída. A operação da porta AND é tal que o HIGH (1) ocorre somente quando todas as entradas são HIGH (1). Mesmo quando uma das entradas for 0, a saída será zero. Suponha que, se A e B são as variáveis de entrada da porta AND e Y é sua saída, então

S = UMA · B

O ponto (·) denota a operação AND, mas normalmente também pode ser escrito como Y = AB. As duas portas AND de entrada construídas usando os diodos são mostradas abaixo, nas quais A e B representam as entradas e Y a saída. O símbolo lógico da porta AND também é mostrado abaixo –

Fig. 4: Imagem mostrando o símbolo e circuito da porta AND

Se A = 0 e B = 0, ambos os diodos conduzem porque estão polarizados diretamente, portanto a saída Y = 0. Se A = 0 e B = 1, o diodo D1 conduz porque estão polarizados diretamente e, portanto, a saída Y = 0. Se A = 1 e B = 0, o diodo D2 conduz porque está polarizado diretamente e, portanto, a saída Y = 0. Se A = 1 e B = 1, ambos os diodos não conduzem porque estão polarizados reversamente, e, portanto, a saída Y = 1. A saída de uma porta AND para duas variáveis booleanas pode ser representada pela seguinte tabela verdade –

Fig. 5: Tabela Verdade da Porta AND

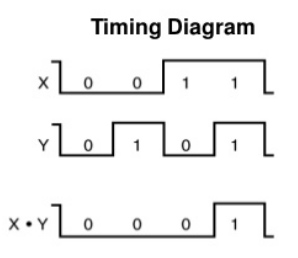

A tabela verdade para a porta AND pode ser representada graficamente pelo seguinte diagrama de tempo –

Fig. 6: Diagrama de temporização da porta AND

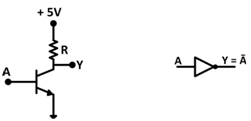

NÃO Portão –

A porta NOT executa a função lógica básica chamada Inversão ou complementação. O objetivo desta porta é converter um nível lógico no nível lógico oposto. Possui uma entrada e uma saída. Quando o nível Alto é aplicado na entrada o nível baixo aparece na saída e vice-versa. Uma porta NOT construída usando um transistor é mostrada abaixo, onde A representa a entrada e Y representa a saída. O símbolo lógico da porta NOT também é mostrado abaixo –

Fig. 7: Imagem mostrando o símbolo e circuito da porta NOT

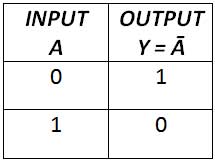

Quando a entrada está em nível ALTO, o transistor está no estado LIGADO e a saída está em nível BAIXO. Quando a entrada está em BAIXO, o transistor está no estado DESLIGADO e a saída está em ALTO. A saída de uma porta NOT pode ser representada pela seguinte tabela verdade –

Fig. 8: Tabela Verdade da Porta NOT

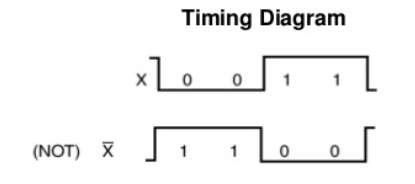

A tabela verdade para a porta NOT pode ser representada graficamente pelo seguinte diagrama de temporização –

Fig. 9: Diagrama de temporização da porta NOT

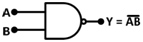

Porta NAND –

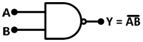

A porta NAND executa a função lógica que é a combinação serial das portas NOT e AND. Possui duas ou mais entradas e apenas uma saída. O símbolo lógico para a porta NAND é mostrado abaixo –

Fig. 10: Imagem mostrando o símbolo e circuito da porta NAND

Em uma porta NAND, quando todas as entradas estão em nível ALTO, a saída é BAIXA. Quando qualquer uma das entradas é BAIXA, a saída é ALTA. A saída de uma porta NAND para duas variáveis booleanas pode ser representada pela seguinte tabela verdade –

Fig. 11: Tabela Verdade da Porta NAND

A tabela verdade para a porta NAND pode ser representada graficamente pelo seguinte diagrama de tempo –

Fig. 12: Diagrama de temporização da porta NAND

Portão NOR –

A porta NOR executa a função lógica que é a combinação serial das portas NOT e OR. Possui duas ou mais entradas e apenas uma saída. O símbolo lógico para a porta NOR é mostrado abaixo –

Fig. 13: Imagem mostrando o símbolo e o circuito da porta NOR

Numa porta NOR, quando todas as entradas estão em nível BAIXO, a saída é em nível ALTO. Quando qualquer uma ou ambas as entradas são ALTAS, a saída é BAIXA. A saída de uma porta NOR para duas variáveis booleanas pode ser representada pela seguinte tabela verdade –

Fig. 14: Tabela Verdade da Porta NOR

A tabela verdade para a porta NOR pode ser representada graficamente pelo seguinte diagrama de temporização –

Fig. 15: Diagrama de temporização da porta NOR

EXCLUSIVO OU (Ex – OU) Portão –

Uma porta OR exclusiva é uma porta com duas ou mais entradas e saídas. A saída de uma porta XOR de duas entradas assume um estado HIGH se uma e apenas uma entrada assume um estado HIGH, ou seja, a saída é HIGH apenas se a entrada A ou entrada B for HIGH e a saída for LOW quando ambas as entradas estiverem em HIGH ou BAIXO. O símbolo lógico do XOR é mostrado abaixo –

Fig. 16: Imagem mostrando o símbolo e circuito da porta XOR

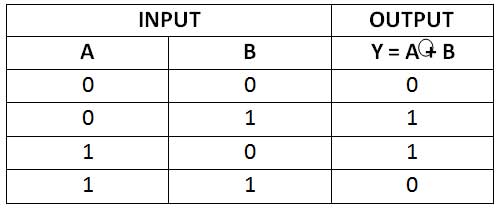

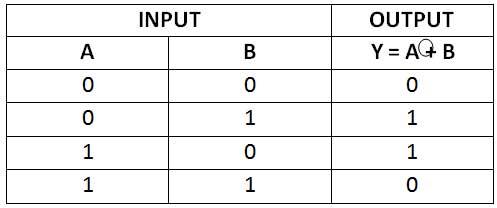

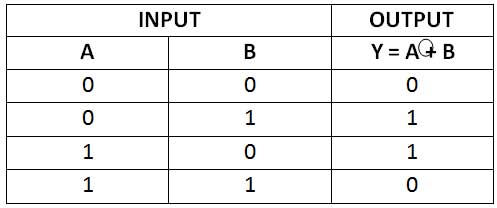

A saída de uma porta XOR para duas variáveis booleanas pode ser representada pela seguinte tabela verdade –

Fig. 17: Tabela Verdade da Porta XOR

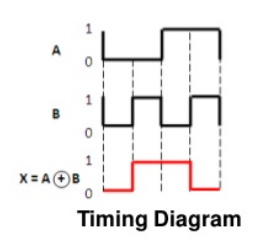

A tabela verdade da porta XOR mostra que a saída é HIGH quando qualquer ummas nem todas as entradas são 1 e quando os dois as entradas são iguais, ou seja, 0 ou 1, a saída é BAIXA. Este recurso exclusivo elimina a semelhança com a porta OR. A tabela verdade para a porta XOR pode ser representada graficamente pelo seguinte diagrama de temporização –

Fig. 18: Diagrama de temporização da porta XOR

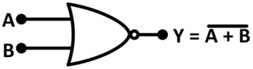

Exclusivo – Portão NOR (XNOR) –

A porta XNOR executa a função lógica que é a combinação serial das portas NOT e XOR. A saída de uma porta XNOR assume um estado HIGH se todas as entradas assumirem o estado HIGH ou o estado LOW. Se alguma das entradas tiver um estado lógico diferente, a saída da porta XNOR será BAIXA. O símbolo lógico do XNOR é mostrado abaixo –

Fig. 19: Imagem mostrando o símbolo e circuito da porta XNOR

A saída de uma porta XNOR para duas variáveis booleanas pode ser representada pela seguinte tabela verdade –

Fig. 20: Tabela Verdade do Portão XNOR

A tabela verdade para a porta XNOR pode ser representada graficamente pelo seguinte diagrama de temporização –

Fig. 21: Diagrama de temporização da porta XNOR

Essas portas lógicas são os blocos de construção de qualquer circuito digital. No próximo tutorial, aprenda sobre teoremas de álgebra booleana e como um expressão booleana pode ser minimizado para Minterms e Maxterms, portanto, pode ser implementado por interconexão de dois níveis de portas lógicas universais (NAND e NOR).