No tutorial anterior, os circuitos aritméticos combinacionais básicos como meio somador, somador completo, meio subtrator e subtrator completo foram discutidos em detalhes. Agora, neste tutorial, serão consideradas a tabela verdade e a derivação das expressões booleanas para todos esses circuitos. Com as expressões booleanas derivadas, todos esses circuitos serão projetados de forma prática usando CIs digitais.

Conforme discutido no tutorial anterior, o meio somador pode ser construído usando uma porta EX-OR e a porta AND. O somador completo pode ser construído usando uma porta OR, duas portas EX-OR e duas portas AND. O meio subtrator pode ser construído usando uma porta EX-OR, uma porta NOT e uma porta AND. O subtrator completo pode ser construído com uma porta OR, duas portas EX-OR, duas portas AND e duas portas NOT. Portanto, para testar todos os circuitos, são necessárias duas portas AND, duas portas EX-OR, duas portas NOT e uma porta OR. Para a porta AND, pode ser usado o IC 7408, que possui quatro portas AND integradas. Para a porta OR, pode ser usado o 7432 IC, que possui quatro portas OR integradas. Para a porta EX-OR, pode ser usado o IC 7486, que possui quatro portas EX-OR integradas. Para porta NOT, pode ser usado o IC 7404, que possui seis portas NOT embutidas. A entrada para os circuitos digitais construídos a partir desses ICs pode ser fornecida por uma fonte DC de 2 V, enquanto a tensão de alimentação para os ICs pode ser fornecida por uma fonte DC de 5 V. A fonte de 5V DC pode ser construída usando uma bateria e 7805 IC. A mesma tensão pode ser reduzida para entradas usando um resistor variável. A saída pode ser verificada conectando LEDs nos respectivos pinos de saída digital.

Então, vamos começar a testar os circuitos combinacionais básicos com CIs digitais mencionados acima.

Diagramas de circuito –

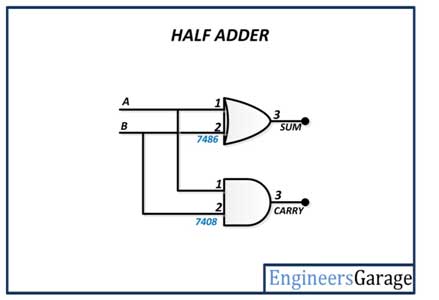

O Meio somador tem o seguinte diagrama de circuito –

Fig. 1: Diagrama de circuito do meio somador

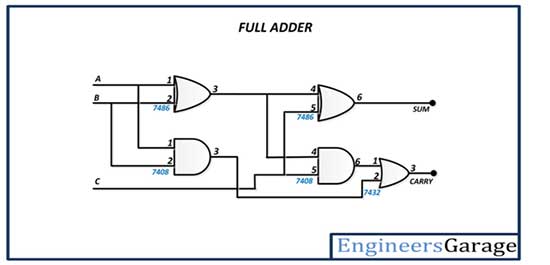

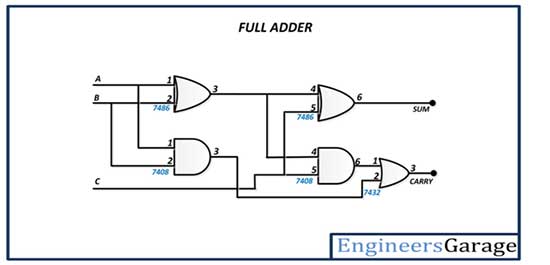

O Somador completo tem o seguinte diagrama de circuito –

Fig. 2: Diagrama de Circuito do Somador Completo

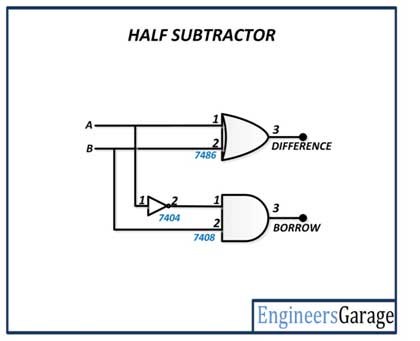

O meio subtrator tem o seguinte diagrama de circuito –

Fig. 3: Diagrama de Circuito do Meio Subtrator

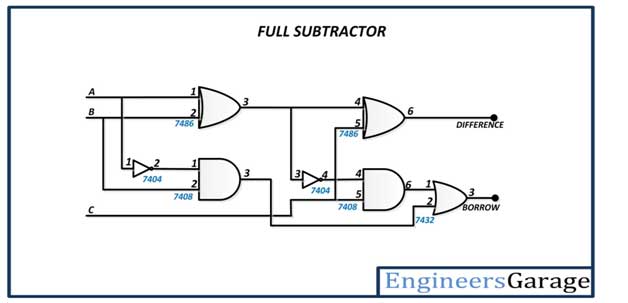

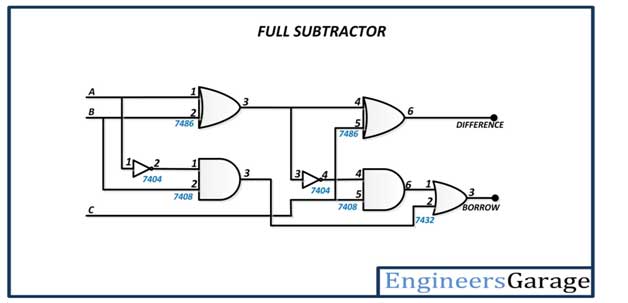

O subtrator completo tem o seguinte diagrama de circuito –

Fig. 4: Diagrama de Circuito do Subtrator Completo

Conexões de Circuito –

Todos os circuitos aritméticos combinacionais são construídos interconectando as portas lógicas. Cada circuito combinacional tem sua própria tabela verdade, onde cada saída está ligada às entradas por alguma função booleana. Os circuitos são construídos interconectando os ICs da porta lógica. Os seguintes ICs de porta lógica são usados na construção dos circuitos –

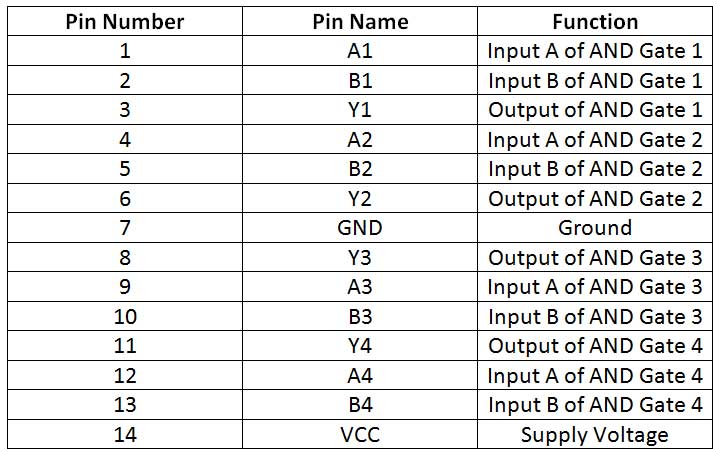

7408 CI – O IC 7408 possui portas AND quádruplas de 2 entradas. O IC tem a seguinte configuração de pinos –

Fig. 5: Tabela listando a configuração dos pinos do 7408 IC

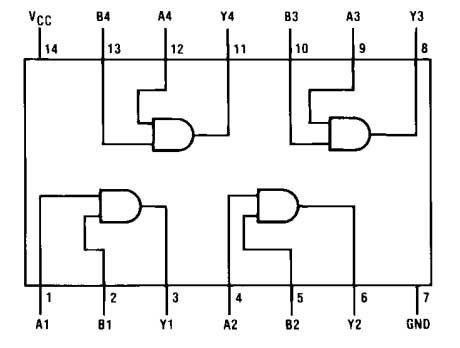

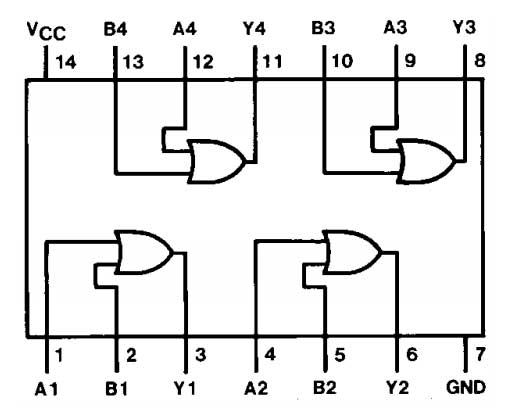

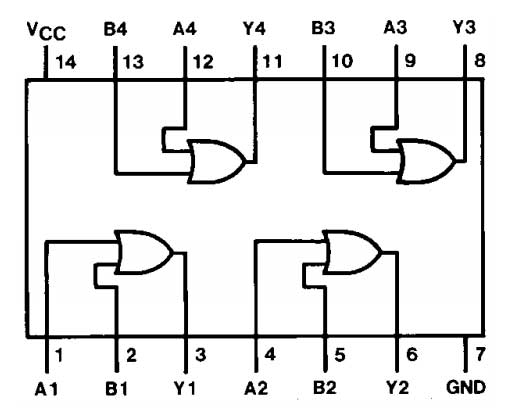

O IC tem o seguinte diagrama de pinos –

Fig. 6: Diagrama de pinos do 7408 IC

O IC requer uma tensão de alimentação de 5V que pode ser tolerada até 7V. A tensão nas entradas das portas AND deve ser 2V para lógica alta e 0V para lógica baixa. A saída das portas AND possui uma tensão de 3,4 V para lógica alta e 0,2 V para lógica baixa. O IC opera em sistema lógico positivo. O atraso de propagação durante o trânsito do nível BAIXO para o ALTO na saída é de 27 ns, enquanto o atraso de propagação durante o trânsito do nível ALTO para o BAIXO na saída é de 19 ns.

7432 CI – O IC 7432 possui portas OR quádruplas de 2 entradas. O IC tem a seguinte configuração de pinos –

Fig. 7: Tabela listando a configuração dos pinos do 7432 IC

O IC tem o seguinte diagrama de pinos –

Fig. 7: Diagrama de pinos do 7432 IC

O IC requer uma tensão de alimentação de 5V que pode ser tolerada até 7V. A tensão nas entradas das portas OR deve ser 2V para lógica alta e 0V para lógica baixa. A saída das portas OR possui tensão de 3,4 V para lógica alta e 0,35 V para lógica baixa. O IC opera em sistema lógico positivo. O atraso de propagação durante o trânsito do nível BAIXO para o ALTO na saída é de 3 a 15 ns, enquanto o atraso de propagação durante o trânsito do nível ALTO para o BAIXO na saída também é de 3 a 15 ns.

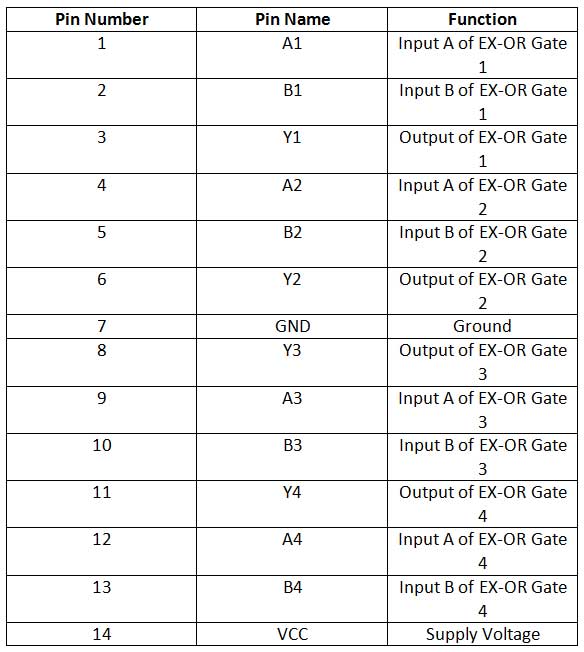

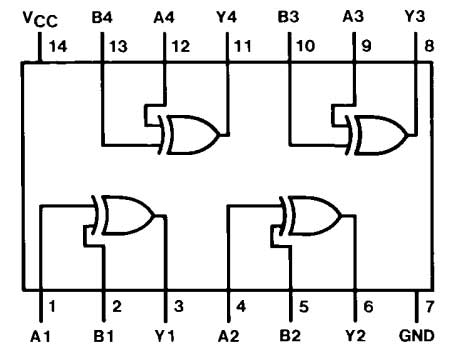

7486 CI – O IC 7486 possui portas EX-OR quádruplas de 2 entradas. O IC tem a seguinte configuração de pinos –

Fig. 8: Tabela listando a configuração dos pinos do 7486 IC

O IC tem o seguinte diagrama de pinos –

Fig. 9: Diagrama de pinos do 7486 IC

O IC requer uma tensão de alimentação de 5V que pode ser tolerada até 7V. A tensão nas entradas das portas EX-OR deve ser 2V para lógica alta e 0V para lógica baixa. A saída das portas EX-OR possui tensão de 3,4 V para lógica alta e 0,2 V para lógica baixa. O IC opera em sistema lógico positivo. O atraso de propagação durante a transição do nível BAIXO para o nível ALTO na saída é de 23 ns se outras entradas forem baixas e 30 ns se outras entradas forem altas, enquanto o atraso de propagação durante a transição do nível ALTO para o nível BAIXO na saída é de 17 ns se outras entradas forem baixas e 22 ns se outras entradas forem altas.

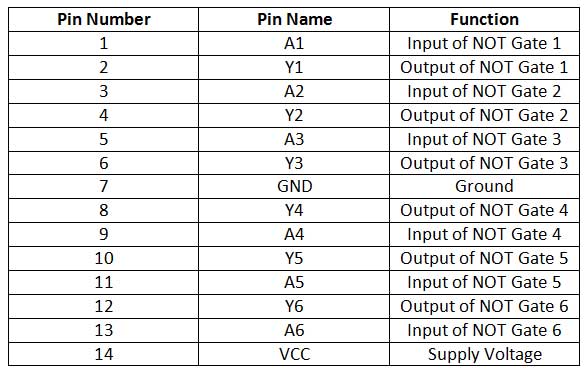

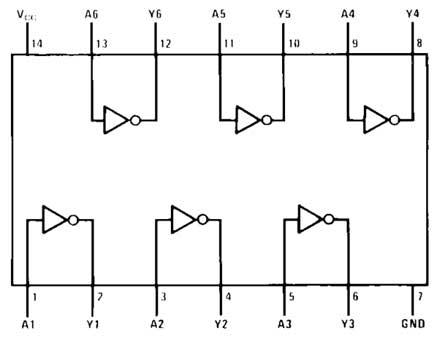

7404 CI – O IC 7404 possui seis portas inversoras. O IC tem a seguinte configuração de pinos –

Fig. 10: Tabela listando a configuração dos pinos do 7404 IC

O IC tem o seguinte diagrama de pinos –

Fig. 11: Diagrama de pinos do 7404 IC

O IC requer uma tensão de alimentação de 5V que pode ser tolerada até 7V. A tensão nas entradas das portas NOT deve ser de 2 V para lógica alta e 0,8 V para lógica baixa. A saída das portas NOT possui tensão de 3,4 V para lógica alta e 0,2 V para lógica baixa. O IC opera em sistema lógico positivo. O atraso de propagação durante o trânsito do nível BAIXO para o ALTO na saída é de 22 ns, enquanto o atraso de propagação durante o trânsito do nível ALTO para o BAIXO na saída é de 15 ns.

Deve-se observar que os ICs selecionados possuem níveis de tensão de entrada, saída e alimentação compatíveis. Eles são retirados de uma família comum (série 74XX) de CIs digitais.

O meio somador é construído conectando as entradas a uma porta EX-OR (pinos 1 e 2 do 7486 IC) e uma porta AND (pinos 1 e 2 do 7408 IC). O bit Sum é extraído da saída da porta EX-OR (pino 3 do 7486 IC) e o carry é extraído da saída da porta AND (pino 3 do 7408 IC).

O somador completo é construído conectando as entradas a uma porta EX-OR (pinos 1 e 2 do 7486 IC) e uma porta AND (pinos 1 e 2 do 7408 IC). A saída da primeira porta EX-OR (pino 3 do 7486 IC) é conectada à entrada da segunda porta EX-OR (pino 4 do 7486 IC) e à entrada da segunda porta AND (pino 4 do 7408 IC). A entrada Carry é conectada a outra entrada da segunda porta EX-OR (pino 5 do 7486 IC) e outra entrada da segunda porta AND (pino 5 do 7408 IC). O bit de soma é extraído da saída da segunda porta EX-OR (pino 6 do 7486 IC). A saída da segunda porta AND (pino 6 do 7408 IC) é conectada a uma entrada da porta OR (pino 1 do 7432 IC) e a saída da primeira porta AND (pino 3 do 7408 IC) é conectada a outra entrada da porta OR ( pino 2 do 7432 IC). A execução é obtida da saída da porta OR (pino 3 do 7432 IC).

O meio subtrator é construído conectando as entradas a uma porta EX-OR (pinos 1 e 2 do 7486 IC) e conectando uma entrada à entrada da porta NOT (pino 1 do 7404 IC) e uma diretamente à entrada de uma porta AND (pino 2 do 7408 IC). A saída da porta NOT (pino 2 do 7404 IC) é conectada à entrada da porta AND (pino 1 do 7408 IC). O bit de diferença é extraído da saída da porta EX-OR (pino 3 do 7486 IC) e o empréstimo é extraído da saída da porta AND (pino 3 do 7408 IC).

O subtrator completo é construído conectando as entradas à primeira porta EX-OR (pinos 1 e 2 do 7486 IC) e conectando uma entrada à entrada da primeira porta NOT (pino 1 do 7404 IC) e uma diretamente à entrada da primeira porta AND. porta (pino 2 do 7408 IC). A saída da primeira porta NOT (pino 2 do 7404 IC) é conectada à entrada da primeira porta AND (pino 1 do 7408 IC). A saída da primeira porta EX-OR (pino 3 do 7486 IC) é conectada à entrada da segunda porta EX-OR (pino 4 do 7486 IC) e à entrada da segunda porta NOT (pino 3 do 7404 IC). A entrada Carry é conectada a outra entrada da segunda porta EX-OR (pino 5 do 7486 IC) e outra entrada da segunda porta AND (pino 5 do 7408 IC). O bit de diferença é extraído da saída da segunda porta EX-OR (pino 6 do 7486 IC). A saída da segunda porta AND (pino 6 do 7408 IC) é conectada a uma entrada da porta OR (pino 1 do 7432 IC) e a saída da primeira porta AND (pino 3 do 7408 IC) é conectada a outra entrada da porta OR ( pino 2 do 7432 IC). O empréstimo é retirado da saída da porta OR (pino 3 do 7432 IC).

Como funciona o circuito –

Cada circuito combinacional possui sua própria tabela verdade e respectivas expressões booleanas para as saídas. Os circuitos construídos acima e suas saídas esperadas são discutidos abaixo –

Meio Somador

O somador binário é o circuito aritmético básico, pois a operação de somar números binários é uma tarefa fundamental na computação. A adição binária segue as seguintes regras –

0 + 0 = 0

1 + 0 = 1

0 + 1 = 1

1 + 1 = 10

Nas três primeiras operações, cada adição binária dá a soma como um bit, ou seja, 0 ou 1. Mas a quarta operação de adição dá uma soma que consiste em dois dígitos binários. Nesse caso, o bit menos significativo é chamado de bit de soma, enquanto o bit mais significativo é chamado de bit de transporte.

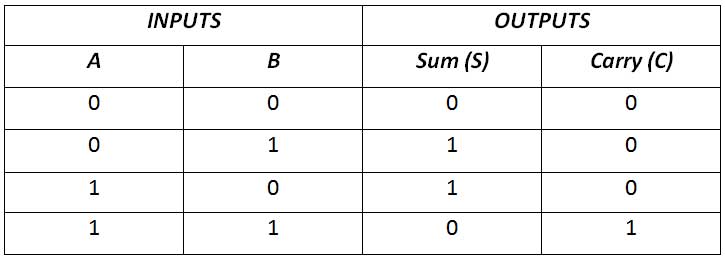

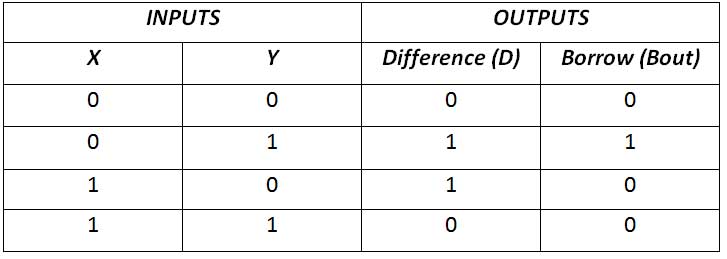

O meio somador tem a seguinte tabela verdade –

Fig. 12: Tabela Verdade do Meio Somador

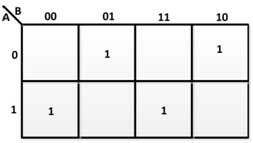

A partir da tabela verdade acima, os seguintes mapas K são desenhados para derivar as expressões booleanas para a saída de soma e transporte –

Fig. 13: K-Map para Soma em Half-Adder

Fig. 14: K-Map para execução em Half-Adder

Portanto, as expressões booleanas para a saída Sum and Carry são as seguintes –

SOMA = A'B + AB' ou SOMA = A B

B

CARREGAR = AB

Portanto, o somador binário construído neste projeto fornece uma soma com carry. Este meio somador tem duas entradas para os dois bits a serem somados e duas saídas, uma da soma 'S' e outra do transporte 'c' para a posição do somador mais alto. No circuito para meio somador, o sinal de transporte da adição dos bits menos significativos é retirado da saída da porta AND enquanto a soma é retirada da saída da porta EX-OR.

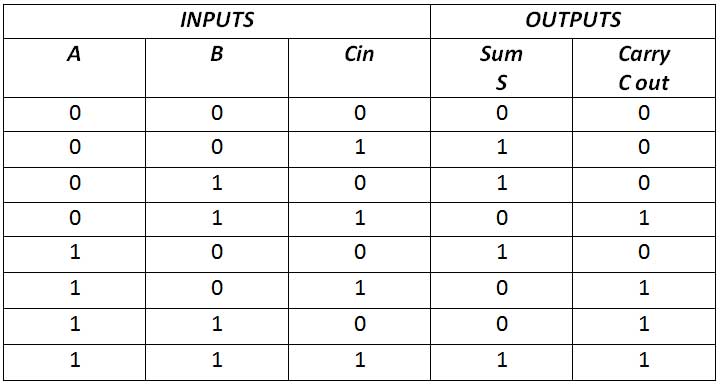

Somador completo

Somador completo é um circuito combinacional que forma a soma aritmética da entrada. Consiste em três entradas e duas saídas. Um somador completo é útil para adicionar três bits de cada vez, mas um meio somador não pode fazer isso. O somador completo tem a seguinte tabela verdade –

Fig. 15: Tabela Verdade do Somador Completo

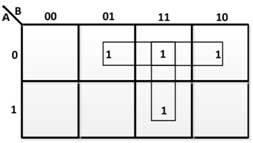

A partir da tabela verdade acima, os seguintes mapas K são desenhados para derivar as expressões booleanas para a saída de soma e transporte –

Fig. 16: K-Map para Soma em Full-Adder

Figura 17: K-Map para execução em Full-Adder

Portanto, as expressões booleanas para a saída Sum and Carry são as seguintes –

SOMA = A'B'C + A'BC' + ABC

= UMA'(B'C  BC') + A(BC')

BC') + A(BC')  AC)

AC)

= UMA'(B  C) + A (B

C) + A (B  C)

C)

= UMA  B

B  C

C

CARREGAR = A'BC + ABC + ABC' + AB'C

= AB + A'BC + AB'C

=AB + C(UMA  B)

B)

= AB + BC + AC

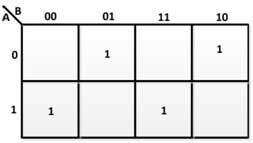

Meio Subtrator

O meio subtrator é construído usando X-OR e as portas AND. O meio subtrator tem duas entradas e duas saídas. As saídas são diferença e empréstimo. A diferença pode ser aplicada usando a porta X-OR, a saída de empréstimo pode ser implementada usando uma porta AND e um inversor. O meio subtrator tem a seguinte tabela verdade –

Fig. 18: Tabela Verdade do Meio Subtrator

A partir da tabela verdade acima, os seguintes mapas K são desenhados para derivar as expressões booleanas para a diferença e a saída emprestada –

Figura 19: K-Map para diferença em meio subtrator

Figura 20: K-Map para empréstimo em meio subtrator

Portanto, as expressões booleanas para saída de Diferença e Empréstimo são as seguintes –

DIFERENÇA = A'B + AB'

EMPRÉSTIMO = A'B

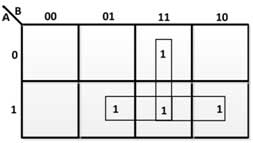

Subtrator Completo

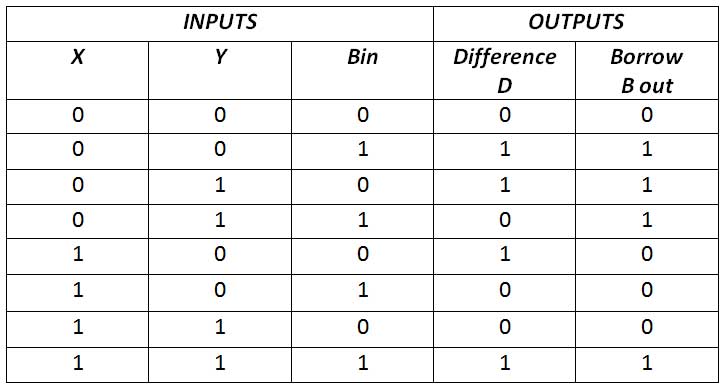

O subtrator completo é uma combinação de portas X-OR, AND, OR, NOT. Em um completo subtrator o circuito lógico deve ter três entradas e duas saídas. Os dois meios subtratores juntos dão um subtrator completo. O subtrator completo tem a seguinte tabela verdade –

Fig. 21: Tabela Verdade do Subtrator Completo

A partir da tabela verdade acima, os seguintes mapas K são desenhados para derivar as expressões booleanas para a diferença e a saída emprestada –

Figura 22: K-Map para diferença em subtrator completo

Figura 23: K-Map para empréstimo em subtrator completo

Portanto, as expressões booleanas para saída de Diferença e Empréstimo são as seguintes –

DIFERENÇA = UMA  B

B  C

C

EMPRÉSTIMO = A'B + BC + A'C

Testando os circuitos –

Os circuitos combinacionais projetados acima podem ser testados fornecendo tensão de alimentação aos ICs por uma bateria por meio do regulador de tensão 7805. A mesma tensão pode ser reduzida para o nível de 2 V usando um resistor variável para lógica ALTA enquanto fornece lógica BAIXA através do terra. Os sinais de saída podem ser verificados conectando LEDs nos pinos de saída de cada circuito combinacional. Os circuitos podem ser verificados verificando as tabelas verdade de cada circuito.

No próximo tutorial, aprenda sobre circuitos conversores de código.

Diagramas de circuito

| Diagrama de Circuito-Adicionador Completo |  |

| Diagrama de Circuito-Subtrator Completo |  |