Nos tutoriais anteriores, todos os circuitos projetados foram circuitos combinacionais. Em circuitos combinacionais, a saída binária depende apenas do estado atual das entradas. Então, na verdade, os circuitos combinacionais têm operação estática. Eles podem ter entrada de um conjunto fixo de valores para os quais a saída resulta em um intervalo definido em qualquer instante de tempo.

Na prática, a maioria dos dispositivos eletrônicos tem operação dinâmica. Eles processam um conjunto de informações binárias recebidas dentro de um intervalo de tempo em diferentes instantes para produzir efetivamente um resultado relevante e em tempo real. Para isso, os dispositivos eletrônicos contêm elementos de memória para armazenar informações digitais recebidas em um instante anterior e possuem circuitos digitais que podem processar informações recebidas no instante presente, bem como no instante anterior, para produzir um resultado relevante. Por exemplo, um computador pode precisar manter os resultados de um cálculo anterior alinhados para um próximo cálculo.

Assim, o tipo de circuito digital cuja saída não depende apenas do estado atual, mas também do estado anterior das entradas, é chamado de circuito sequencial. Os circuitos sequenciais são circuitos combinacionais com feedback de elementos de memória. A qualquer instante, o circuito combinacional dentro de um circuito sequencial recebe a entrada atual e recupera os estados de entrada anteriores dos elementos de memória para realizar a computação. Uma vez concluída a computação, antes que ocorra a próxima computação, a parte combinacional do circuito sequencial armazena os estados de entrada atualmente recebidos nos elementos de memória. Pode-se dizer que os elementos de memória em um circuito sequencial funcionam como um elemento de realimentação. Com elementos de memória à disposição, os circuitos sequenciais são capazes de armazenar, reter e recuperar o estado anterior das entradas ou, digamos, estados das entradas no instante anterior.

Existem dois tipos de circuitos sequenciais –

1) Circuitos Sequenciais Síncronos

2) Circuitos Sequenciais Assíncronos

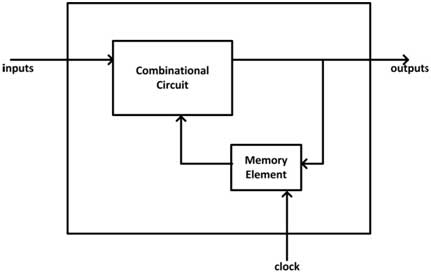

Os dois tipos de circuitos sequenciais diferem no esquema de temporização de seus sinais. Os circuitos sequenciais síncronos operam dados em sinais de relógio periódicos, portanto, operam em dados binários em instantes discretos de tempo. O sinal de relógio periódico é gerado por um dispositivo de temporização denominado gerador de relógio e o sinal de relógio é gerado e recebido como pulsos. O cálculo de dados pelo circuito combinacional do circuito sequencial síncrono, bem como o armazenamento e recuperação de dados dos elementos de memória, é realizado na chegada dos pulsos de clock, ou seja, quando o sinal de clock muda de 0 para 1 em tais circuitos. Enquanto isso, o sinal do relógio volta para 0, o circuito combinacional do circuito síncrono se prepara para o próximo ciclo de computação enquanto os elementos de memória armazenam o estado anterior das entradas e se preparam para que o mesmo seja recuperado na chegada do próximo pulso. Para operação síncrona de circuitos combinacionais e elementos de memória de acordo com o sinal de relógio periódico, o atraso de propagação nas portas lógicas que constroem os respectivos circuitos é controlado de acordo. A taxa na qual o relógio mestre gera os pulsos deve ser lenta o suficiente para permitir que o circuito mais lento responda. Isso limita a velocidade de todos os circuitos. Pode-se dizer que os circuitos síncronos são construídos integrando circuitos combinacionais, elementos de memória e gerador de clock. Um circuito sequencial síncrono pode ser representado pelo seguinte diagrama de blocos –

Fig. 1: Diagrama de blocos de circuitos sequenciais síncronos

Em circuitos sequenciais assíncronos, o feedback dos estados anteriores de entrada para o circuito combinacional pode ocorrer em qualquer instante de tempo, em vez de ser de natureza periódica e, portanto, depende da ordem dos sinais de entrada, e não da ocorrência de qualquer pulso de clock. Nesses circuitos, os elementos de memória são acoplados a circuitos de retardo de tempo, de modo que o feedback do estado anterior das entradas possa ser recebido no instante em que as entradas atuais são recebidas. Na maioria dos casos, o atraso de propagação através das portas nos elementos de memória é suficiente para produzir o atraso de tempo necessário. Nesses circuitos, a capacidade de armazenamento dos elementos de memória também depende do atraso de propagação do sinal. Os circuitos assíncronos podem ser instáveis ou não confiáveis às vezes devido a atrasos sem precedentes nos circuitos ou nas entradas do circuito. Portanto, o projeto de circuitos sequenciais assíncronos sempre requer cautela e detalhes técnicos extras. Assim, pode-se dizer que circuitos sequenciais assíncronos são construídos integrando circuitos combinacionais e elementos de memória com atrasos de tempo definidos na propagação do sinal.

Comparados aos circuitos combinacionais, os circuitos sequenciais são mais lentos, pois precisam sincronizar de acordo com relógio sinal no caso de circuitos síncronos ou deve ter atrasos de tempo definidos no caso de circuitos assíncronos. Os circuitos combinacionais, uma vez que dependem apenas dos estados atuais de entrada, processar os dados imediatamente afetados apenas pelo atraso de propagação dos sinais através das portas.

No entanto, os circuitos sequenciais incorporam os elementos de memória que são uma parte vital de qualquer eletrônica moderna. A maioria dos dispositivos eletrônicos precisa armazenar ou reter dados conforme a necessidade do cálculo. Os circuitos sequenciais, embora tenham velocidade limitada em seu próprio conceito de design, são os circuitos digitais mais abundantes na eletrônica.

Elementos de memória –

Os elementos de memória são essenciais na construção de qualquer circuito sequencial. O elemento de memória mais simples pode armazenar um único bit a qualquer momento. Um grupo desses elementos de memória forma memórias maiores. Existem dois tipos de elementos de memória de armazenamento de bit único – Latches e Flip-Flops. Ambos podem armazenar um único bit por vez.

Os latches são elementos de memória sensíveis ao nível que respondem ao estado 0 ou 1 do sinal, enquanto os flip-flops são elementos de memória sensíveis à transição que respondem à transição do sinal de 0 para 1 e vice-versa. Respondendo às transições de sinal, os flip-flops são chamados de dispositivos sensíveis à borda. Os próprios flip-flops são construídos a partir de travas. Os latches são usados como elementos de memória em circuitos sequenciais assíncronos, mas não podem ser usados em circuitos síncronos. Em circuitos síncronos, os flip-flops são usados como elementos de memória.

Em um estado estável, a saída de um flip-flop permanece 1 ou 0. A saída de um flip-flop muda apenas quando um pulso de clock é recebido por ele. A saída de um flip-flop depende da entrada de dados atual ou do valor atualmente armazenado nele ou de ambos. O circuito combinacional de um circuito síncrono deve estar sincronizado com os pulsos de clock e atingir um estado estável antes que os estados de entrada anteriores sejam passados para serem armazenados nos flip-flops. O circuito deve ser capaz de responder à mudança nos estados dos flip-flops antes que o próximo pulso de clock chegue. Portanto, a duração do pulso de clock precisa ser pré-determinada para o bom funcionamento de um circuito síncrono. Deve-se notar que esses elementos de memória – travas e flip-flops retêm informações binárias até receberem energia. Caso haja um corte de energia, os dados retidos por eles naquele momento são perdidos.

Travas –

As travas são dispositivos de memória sensíveis ao nível. Eles são usados em circuitos sequenciais assíncronos. Eles também são os blocos de construção dos chinelos. Existem três tipos de travas –

1) Trava SR

2) Trava S'R'

3) D Trava

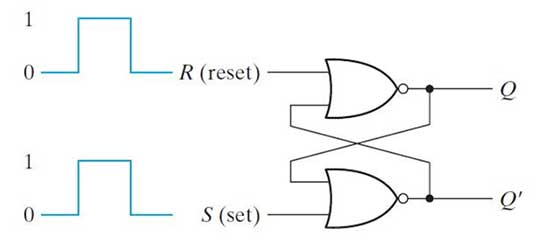

Trava SR – A trava SR é construída por duas portas NOR acopladas cruzadamente. Possui duas entradas – set (S) e reset (R) enquanto duas saídas Q e Q'. O Q e Q' são normalmente complementares um do outro. Quando o conjunto de entrada é 1 e o reset de entrada é 0, a saída Q se torna 1 e Q' se torna 0. Quando o conjunto de entrada é 0 e o reset de entrada é 1, a saída Q se torna 0 e Q' se torna 1. Quando ambos definidos e reset são 0, o flip-flop SR retém o estado de saída, ou seja, se anteriormente Q se tornou 1 e Q' se tornou 0, os mesmos estados serão retidos enquanto set e reset forem 0. Da mesma forma, se anteriormente Q se tornou 0 e Q' se tornou 1, os mesmos estados serão mantidos enquanto tanto set quanto reset forem 0. Se set e reset forem 1, então Q e Q' se tornarão 0, o que é proibido. Portanto, se o set ou o reset for 1 altera o bit armazenado pela trava SR, se ambos se tornarem 0, o bit armazenado é retido enquanto ambos sendo 1 é uma condição proibida. A trava SR pode ser construída por portas NOR da seguinte forma –

Fig. 2: Diagrama de porta lógica da trava SR

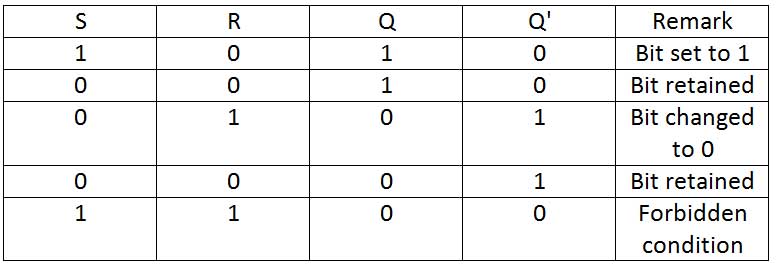

A operação de uma trava SR pode ser resumida pela seguinte tabela de funções –

Fig. 3: Tabela Verdade da Trava SR

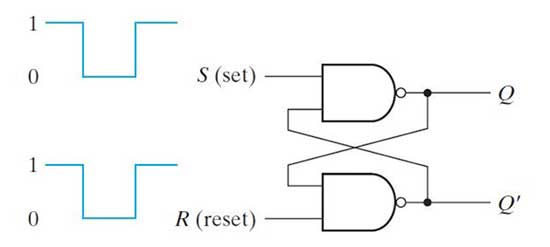

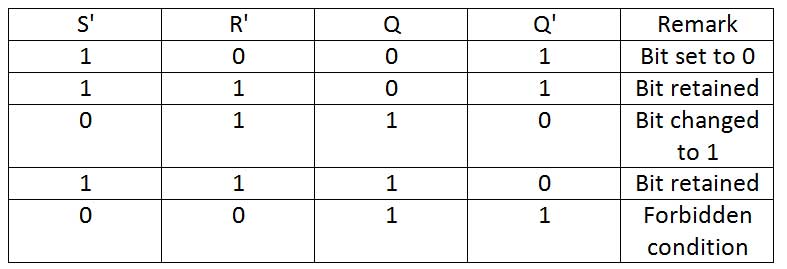

Trava S'R' – A trava S'R' é um tipo de trava SR construída a partir de duas portas NAND acopladas em vez de duas portas NOR acopladas. Na trava S'R', quando o conjunto de entrada é 1 e o reset de entrada é 0, a saída Q se torna 0 e Q' se torna 1. Quando o conjunto de entrada é 0 e o reset de entrada é 1, a saída Q se torna 1 e Q' se torna 0. Quando set e reset são 1, o flip-flop S'R' retém o estado de saída, ou seja, se anteriormente Q tivesse se tornado 0 e Q' tivesse se tornado 1, os mesmos estados serão retidos enquanto set e reset forem 1. Da mesma forma, se anteriormente Q tivesse se tornado 1 e Q' tivesse se tornado 0, os mesmos estados serão mantidos enquanto tanto set quanto reset forem 1. Se set e reset forem 0, então tanto Q quanto Q' se tornarão 1, o que é proibido. Portanto, se o valor definido ou redefinido for 0, o bit armazenado pela trava S'R' será alterado; se ambos se tornarem 1, o bit armazenado será retido, enquanto ambos forem 0 é uma condição proibida. Pode-se observar que a saída do latch S'R' é sempre um complemento da saída do latch SR, por isso recebeu seu nome – latch S'R'. A trava S'R' pode ser construída por portas NAND da seguinte forma –

Fig. 4: Diagrama da porta lógica da trava S'R'

A operação de uma trava S'R' pode ser resumida pela seguinte tabela de funções –

Fig. 5: Tabela Verdade da Trava S'R'

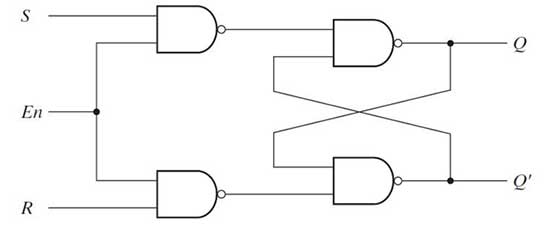

A trava SR ou S'R' pode ter entrada de habilitação adicional para controlar a mudança em seu estado. A entrada de habilitação pode ser adicionada conectando duas portas NAND adicionais ao circuito básico da trava SR como segue –

Fig. 6: Diagrama da porta lógica da trava SR com entrada de habilitação

A trava SR com entrada de habilitação possui a seguinte tabela de funções –

Fig. 7: Tabela verdade da trava SR com entrada de habilitação

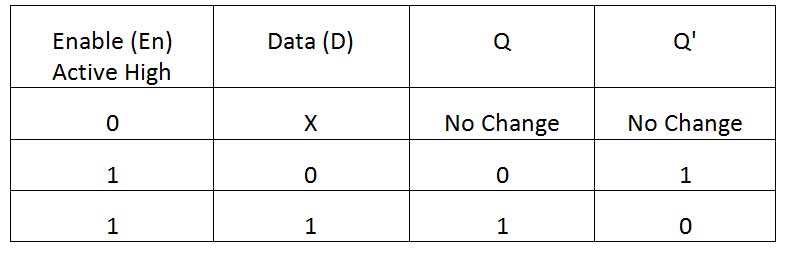

Trava D – D Latch é uma variante do latch SR ou latch S'R' para eliminar a condição proibida de sua tabela de funções. Em um Latch D, existem apenas duas entradas – Dados (D) e Habilitação (En) e há duas saídas Q e Q'. A entrada de habilitação pode ser ativa baixa ou ativa alta. Caso a entrada de habilitação esteja ativa alto, se houver 0 na entrada de habilitação, os dados serão retidos pela trava e não serão transferidos para as saídas. Quando a entrada de habilitação é definida como 1, se os dados de entrada forem 0, Q se torna 0 e Q' se torna 1, enquanto se os dados de entrada forem 1, Q se torna 1 e Q' se torna 0. Para entrada de habilitação alta ativa, a trava D tem o seguinte tabela de funções –

Fig. 8: Tabela Verdade do Latch Alto D Ativo

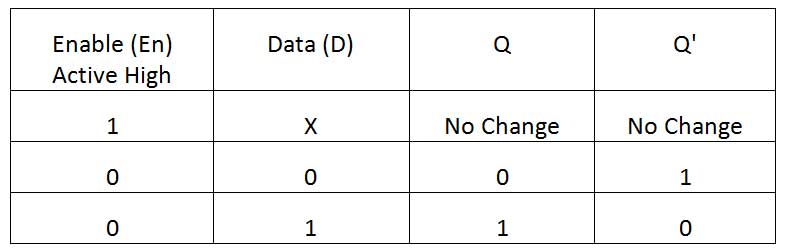

Se a entrada de habilitação estiver ativa em nível baixo, os dados serão retidos pela trava quando a entrada de habilitação estiver definida como 1 e transferidos para a saída quando a entrada de habilitação estiver definida como 0. A entrada de habilitação pode ser tornada ativa em nível baixo conectando uma porta inversora a ela. Com entrada de habilitação baixa ativa, o D Latch possui a seguinte tabela de funções –

Fig. 9: Tabela Verdade do Latch Ativo Low D

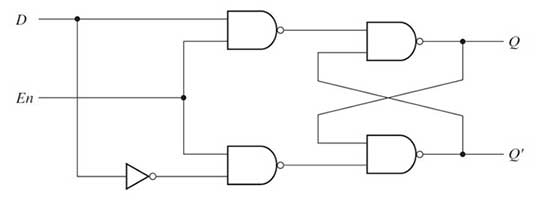

DE ANÚNCIOS A trava é construída acoplando a entrada às portas NAND em uma trava SR com entrada Enable. Ao acoplar as portas NAND em primeiro No nível da implementação da porta lógica do latch D, a entrada de dados é diretamente conectada à entrada Set (S) do latch SR enquanto é conectada através de um inversor à entrada Reset (R) do latch SR. Desta forma, quando Data (D) é 0, Set é 0 e Reset é 1, enquanto quando D é 1, Set é 1 e Reset é 0. DE ANÚNCIOS latch tem o seguinte diagrama de porta lógica –

Fig. 10: Diagrama de circuito da trava D

Como em uma latch D, os dados são transferidos para a saída Q quando Enable (En) é definido como 1 em caso de ativo alto ou é definido como 0 em caso de configuração ativa baixa enquanto é retido no estado reverso da habilitação entrada, a trava D também é chamada de trava transparente.

As travas são usadas como elementos de memória em circuitos sequenciais assíncronos. No próximo tutorial, Sandálias de dedo e seus diferentes tipos serão discutidos. Os flip-flops são os elementos de memória usados em circuitos sequenciais síncronos.