No tutorial anterior, noções básicas de circuitos lógicos sequenciais foram discutidos. Foi mencionado que os circuitos sequenciais podem ser de dois tipos – síncronos e assíncronos. Os circuitos sequenciais são diferentes dos circuitos combinacionais na forma como possuem elementos de memória para feedback de estados de entrada anteriores. Os circuitos assíncronos usam travas como elementos de memória. As travas não podem ser usadas como elementos de memória em circuitos síncronos, pois os circuitos síncronos requerem dispositivos sensíveis à transição para operar contra sinais de clock. Assim, para circuitos síncronos, os flip-flops são usados como elementos de memória.

Os próprios flip-flops são construídos sobre travas. Para fazer um flip-flop, a operação do latch básico é modificada fornecendo uma entrada de controle adicional que determina quando o estado do circuito deve ser alterado. Então, basicamente, a trava com a entrada de controle adicional é chamada de flip-flop. A entrada de controle adicional é o relógio ou a entrada de habilitação.

Os flip-flops são categorizados em diferentes tipos, dependendo de como suas entradas e pulsos de clock causam a transição entre dois estados. Existem quatro tipos básicos de flip-flops, como segue –

1) Flip-Flop S – R

2) J – K Flip-Flop

3) D Flip Flop

4) Flip-flop T

Flip-flop SR –

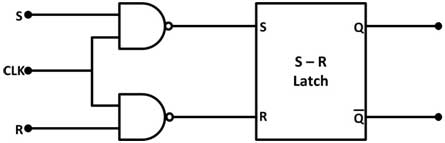

O flip-flop SR é simplesmente o latch SR com entrada de habilitação. A trava SR com entrada Enable foi descrita no tutorial anterior. Este é o flip-flop mais simples. A trava SR é construída por duas portas NOR acopladas cruzadamente. A entrada Enable é adicionada conectando duas portas NAND adicionais ao circuito básico da trava SR. Assim, o flip-flop SR possui duas saídas Q e Q' que são complementares uma da outra e três entradas – Set (S), Reset (R) e Enable (En). O pulso de clock é aplicado à entrada de habilitação. O flip-flop muda de estado somente quando está definido para HIGH (caso a entrada Enable esteja ativa em nível alto) ou quando está definido para LOW (caso a entrada Enable esteja ativa em nível baixo). A entrada de habilitação pode ser ativada em nível baixo conectando uma porta inversora antes dela. O Flip Flop SR possui o seguinte diagrama de porta lógica –

![]()

Fig. 1: Diagrama de porta lógica do flip-flop SR

Ele pode ser representado pelo seguinte diagrama de blocos –

Fig. 2: Diagrama de blocos do flip-flop SR

Opera de acordo com a seguinte tabela de funções –

Figura 3: Tabela verdade do flip-flop SR

Pode-se observar na tabela de funções que quando S = 0 e R = 0 a saída das portas NAND 3 e 4 é forçada a se tornar 1. Portanto, R' e S' serão iguais a 1. Já que S' e R' são a entrada da trava SR básica usando portas NAND, não haverá alteração no estado das saídas. Quando S = 0 e R = 1, uma vez que S = 0, a saída de NAND-3, ou seja, R' = 1 e E = 1, a saída de NAND-4, ou seja, S' = 0. Portanto, Qn+1 = 0 e Qn+1 barra = 1. Isso é chamado reiniciar doença. Quando S = e R = 0. saída de NAND-3, ou seja, R' = 0 e saída de NAND-4, ou seja, S' = 1. Portanto, a saída da trava SR NAND é Qn+1 = 1 e Qn+1 bar = 0. Isso é chamado de condição definida. Como S = 1, R = 1 e E = 1, a saída de ambas as portas NAND 3 e 4 é 0, ou seja, S' = R' = 0. Portanto, a condição proibida ocorrerá na trava NAND básica.

D flip-flop –

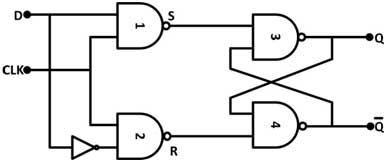

O D Flip Flop é construído a partir da trava D. Ele foi projetado para evitar condições proibidas no flip-flop SR. O flip-flop D (Delay) possui apenas uma entrada chamada entrada de atraso, as duas saídas Q e Ǭ e a entrada Enable para receber pulsos de clock. AD Flip Flop é construído acoplando entradas a portas NAND em um Flip Flop SR. Ao acoplar as portas NAND no primeiro nível da implementação da porta lógica do D Flip Flop, a entrada Data é diretamente conectada à entrada Set (S) do latch SR enquanto é conectada através de um inversor à entrada Reset (R) do a trava SR. Desta forma, quando Data (D) é 0, Set é 0 e Reset é 1, enquanto quando D é 1, Set é 1 e Reset é 0. O flip-flop AD tem o seguinte diagrama de porta lógica –

Fig. 4: Diagrama de porta lógica do flip-flop D

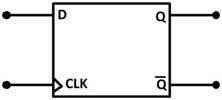

O flip-flop AD pode ser representado pelo seguinte diagrama de porta lógica –

Fig. 5: Diagrama de blocos do flip-flop D

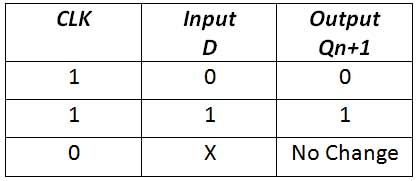

O D Flip Flop opera de acordo com a seguinte tabela de funções –

Figura 6: Tabela verdade do flip-flop D

Pela tabela de funções, pode-se observar que quando a entrada CLK está em nível LOW, a entrada D não tem efeito, pois as entradas set e reset do NAND chinelo de dedo são mantidos em ALTO. Quando o CLK vai para ALTO, a saída Q assumirá o valor da entrada D. Se CLK = 1 e D = 1, a saída da porta NAND -1 vai para 0, que é a entrada da barra S do SR básico baseado em NAND chinelo de dedo e NAND gate-2 vai para 1, que é a entrada da barra R do SR básico baseado em NAND chinelo de dedo. Portanto S bar = 0 e R bar = 1, o chinelo de dedo a saída será 1, ou seja, segue a entrada D. Para CLK = 1 e D = 0, o chinelo de dedo a saída será 0. Se D mudar enquanto CLK estiver HIGH, Q seguirá e mudará rapidamente.

Na tabela de funções fica claro que o próximo estado do flip-flop a qualquer momento (Qn +1) segue o valor da entrada D quando o pulso de clock é aplicado. Como a transferência de dados da entrada para a saída é atrasada, isso é conhecido como flip-flop de atraso (D). O flip-flop D é usado como dispositivo de atraso ou como trava para armazenar 1 bit de informação binária.

Senhor de escravos Chinelo JK –

O flip-flop Master Slave JK foi projetado para evitar condições proibidas no flip-flop SR, além de eliminar o problema de temporização para resposta aos níveis altos e baixos do pulso de clock. O Flip-Flop Master Slave JK é construído conectando dois flip-flops SR em cascata com feedback da saída do segundo para a entrada do primeiro. Dessa forma, o flip-flop Master é acionado por um nível positivo. Mas devido à presença do inversor na linha do clock, o escravo responderá ao nível negativo. Portanto, quando o sinal do clock é 1 (nível positivo), o mestre está ativo e o escravo está inativo. Já quando o clock está em 0 (nível baixo), o escravo está ativo e o mestre está inativo.

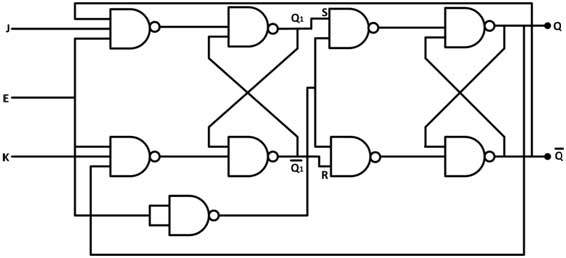

O flip-flop JK tem três entradas J, K e entrada Enable, enquanto duas saídas Q e Q'. O JK Flip Flop possui o seguinte diagrama de porta lógica –

Fig. 7: Diagrama de porta lógica do flip-flop Master Slave JK

Opera de acordo com a seguinte tabela de funções –

Fig. 8: Tabela Verdade do Flip Flop Master Slave JK

Da função mesa pode-se observar que existem quatro saídas possíveis de JK sandálias de dedo como mencionado abaixo –

Caso 1 – J. = K = 0 (Sem alteração): Quando o sinal do clock é 0, o escravo fica ativo e o mestre inativo. Mas, como as entradas S e R não foram alteradas, as saídas escravas também permanecerão inalteradas. Portanto, as saídas não mudarão se J e K forem 0.

Caso 2 – J. = 0 e K = 1 (Reset): Quando o sinal do Relógio é 1, o Mestre está ativo enquanto o escravo está inativo. Portanto, as saídas do mestre tornam-se Q1 = 0 e Q1 bar = 1. Isso significa que S torna-se 0 e R torna-se 1. Quando o sinal do Clock é 0, o Escravo está ativo enquanto o mestre está inativo. Portanto, as saídas do escravo tornam-se Q = 0 e Q bar = 1. Novamente, quando o sinal do relógio é 1, o Mestre está ativo e o escravo está inativo. Portanto, mesmo com as saídas alteradas (Q = 0 e Q bar = 1) realimentadas para o mestre, sua saída será Q1 = 0 e Q1 bar = 1. Isso significa que S se torna 0 e R se torna 1. Portanto, com sinal de clock estando 0 e o escravo se tornando ativo, as saídas do escravo permanecerão Q = 0 e Q bar = 1. Assim, há uma saída estável do Mestre e do Escravo.

Caso 3 – J. = 1 e K = 0 (Set): Quando o sinal do Clock é 1, o Mestre está ativo e o escravo está inativo. Portanto, as saídas do mestre tornam-se Q1 = 1 e Q1 bar = 0. Isso significa que S é definido como 1 e R definido como 0. Quando o sinal do Clock é 0, o Escravo está ativo e o Mestre está inativo. Portanto, as saídas do escravo tornam-se Q = 1 e Q bar = 0. Novamente, quando o sinal do clock é 1, pode-se ver que as saídas do escravo estão estabilizadas em Q = 1 e Q bar = 0.

Caso 4 – J. = K = 1 (Alternar): Quando o sinal do Relógio é 1, o Mestre está ativo e o escravo está inativo. As saídas do master serão alternadas. Então S e R também serão invertidos. Quando o sinal do Clock é 0, o Escravo está ativo e o Mestre está inativo. As saídas do escravo serão alternadas. Essas saídas alteradas são devolvidas às entradas mestres. Mas, quando o sinal do clock é 0, o mestre ainda está inativo. Portanto, ele não responde a essas saídas alteradas. Isso evita a alternância múltipla que leva à condição de corrida ao redor. O flip-flop mestre escravo é útil para evitar a condição de corrida do flip-flop SR.

Chinelo T –

O flip-flop T ou Toggle Flip Flop altera sua saída em cada transição do clock. É outro flip-flop básico que possui apenas uma única entrada de dados (T), uma entrada de clock e duas saídas Q e Ǭ. O flip-flop tipo T é construído a partir do flip-flop JK conectando suas entradas J e K. O T representa a capacidade do flip-flop de alternar ou complementar seu estado. AT Flip Flop é representado pelo seguinte diagrama de blocos –

Fig. 9: Diagrama de blocos do flip-flop T

O T Flip Flop pode ser construído conectando as entradas J e K do JK chinelo de dedo junto. Dessa forma, o JK chinelo de dedo pode entrar apenas no estado sem alteração ou no estado de alternância. O T Flip Flop é construído a partir do JK Chinelo de dedo como se segue –

Fig. 10: Diagrama de porta lógica do flip-flop T

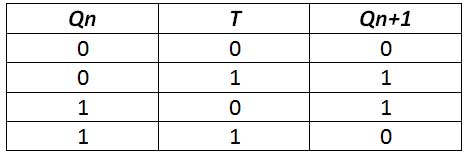

O T Flip Flop opera de acordo com a seguinte tabela de funções –

Fig. 11: Tabela verdade do flip-flop T

Na tabela de funções, pode-se observar que quando a entrada T está em 0 estado (ou seja, J = K = 0) antes de relógio pulso, a saída Q não mudará com cronometrando. Quando a entrada T é definida para 1 nível (ou seja, J = K = 1) antes de cronometrando, a saída estará no estado Ǭ após o clock. Em outras palavras, se a entrada T for lógica 1 e o dispositivo estiver sincronizado, a saída mudará de estado independentemente de qual saída estava antes da entrada. cronometrando. Então, quando T = 0, então Qn+1 = Qn, ou seja, o próximo estado é igual ao estado atual e nenhuma mudança ocorre. Quando T = 1, então Qn+1 = Ǭn , ou seja, o estado do flip-flop é complementado. Isso é chamado de alternância, então o chinelo de dedo recebeu o nome de flip-flop T.

Flip-Flops são parte essencial de qualquer circuito síncrono. Eles podem armazenar um único bit de cada vez. Os grupos de flip-flops são usados para armazenar dados em circuitos síncronos práticos. No próximo tutorial, aprenda sobre registros.